# PHYSICS-BASED THERMAL IMPEDANCE MODELS FOR THE SIMULATION OF SELF-HEATING IN SEMICONDUCTOR DEVICES AND CIRCUITS

By

JONATHAN SCOTT BRODSKY

A DISSERTATION PRESENTED TO THE GRADUATE SCHOOL

OF THE UNIVERSITY OF FLORIDA IN PARTIAL FULFILLMENT

OF THE REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

UNIVERSITY OF FLORIDA

1997

This work is dedicated to my parents,

Lawrence and Jeraldine,

my brother Matthew and sister Alexandra.

#### ACKNOWLEDGEMENTS

First, I wish to express my deepest gratitude to my advisor Dr. Robert M. Fox. His constant support and patient guidance provided a clear path for my research. It is both a pleasure and a privilege to have worked with Dr. Fox. I thank Drs. Mark E. Law and Jerry G. Fossum for extending their expertise and help to my unending questions. I would also like to thank Drs. William R. Eisenstadt, John G. Harris and Chen-Chi Hsu for their willingness to serve on my supervisory committee. I am also very grateful to Mary Turner for all of her help throughout my graduate career.

I would like to acknowledge and thank the Semiconductor Research Corporation (SRC) for the financial support that made this research possible. I am also grateful to Dr. Surya Veeraraghavan for his guidance and friendship during my internship at Motorola.

I would like to thank the "TCAD elders", and now my friends, Keith Green, Dongwook Suh, Ping-Chin Yeh, Haeseok Cho, Chih-Chuan Lin, Ming-Chang Liang and Scott Miller, for helping me get comfortable in my new surroundings and setting the standard of excellence.

I am also grateful to my good friends/workmates/"happy hour buddies" Srinath Krishnan, Samir Chaudhry, David Zweidinger, Omer Dokumaci, Ming-Yeh Chuang, Dukhyun Chang, Susan Earles, Hernan Rueda, Glenn Workman and Meng-

Hsueh Chiang, for all of the enlightening discussions, the Friday lunch tradition and the weekend adventures.

There is a very special group of individuals who have my admiration and love for the friendships they have given me. I would like to thank my best friends Douglas Weiser, Martin Weiss, Stephen Cea, Edward Cometz and Peter Lynch.

I can not completely express the role my family has played in my life and in the completion of this dissertation. For simple words seem to diminish their unconditional and unending love and support. I owe everything I have, everything I have done and everything I am, to my family. I give my deepest love to my parents, Jeraldine and Lawrence Brodsky, my brother Matthew and my sister Alexandra.

Finally, I am grateful to all of the wonderful friends that I met in Gainesville for making this period of my life truly enjoyable.

## TABLE OF CONTENTS

| ACKN  | OWLEDGEMENTS iii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ABSTI | RACT viii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1     | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|       | 1.1Self-Heating Effects in Semiconductor Devices11.1.1Bipolar Transistors31.1.2Field-Effect Transistors61.2Self-Heating Effects in Semiconductor Circuits81.2.1Small-Signal Circuit Performance81.2.2Large-Signal Circuit Performance111.3Self-Heating Effects in Parameter Extraction121.4The Simulation of Self-Heating Effects131.5Thermal Equivalent Circuits161.6The Need for Physics-Based Thermal Impedance Models201.7Organization25                                                                                                                              |

| 2     | A THREE-DIMENSIONAL THERMAL IMPEDANCE MODEL FOR JUNCTION-ISOLATED BIPOLAR TRANSISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|       | 2.1 Introduction272.2 Derivation of the Single-Emitter BJT/HBT Thermal Impedance Model282.2.1 Modification for Finite Wafer Thickness392.2.2 Effects of Interconnect Metallization on the Thermal Impedance432.2.3 A Model for the Thermal Impedance of the Emitter Interconnect492.2.4 Effects of Isolation Structures on the Thermal Impedance522.3 Verification of the Single-Emitter Thermal Impedance Model612.4 Derivation of the Multiple-Emitter BJT/HBT Thermal Impedance Model662.5 Verification of the Multiple-Emitter Thermal Impedance Model722.6 Summary76 |

| 3     | A CIRCUIT MODEL FOR THERMAL COUPLING AND A LUMPED ELECTROTHERMAL MODEL FOR BULK MULTIPLE-EMITTER BIPOLAR TRANSISTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | 3.3 A Lumped Electrothermal Model for Multiple-Emitter BJT/HBT's                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4 | A THREE-DIMENSIONAL THERMAL IMPEDANCE MODEL FOR VERTICAL BIPOLAR TRANSISTORS FABRICATED WITH FULL DIELECTRIC ISOLATION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 4.1 Introduction1034.2 Derivation of the DIBJT Thermal Impedance Model1064.2.1 Derivation of the Buried-Oxide Heat-Transfer Coefficient1164.2.2 Derivation of the Trench Heat-Transfer Coefficient1204.2.3 Effects of Interconnect Metallization on the Thermal Impedance1264.2.4 A Model for the Thermal Impedance of the Emitter Interconnect1294.3 Verification of the DIBJT Thermal Impedance Model1324.4 Derivation of a Compact DIBJT Thermal Resistance Model1344.5 Verification of the DIBJT Thermal Resistance Model1464.6 Summary149 |

| 5 | A THREE-DIMENSIONAL THERMAL IMPEDANCE MODEL FOR BULK METAL-OXIDE-SEMICONDUCTOR FIELD-EFFECT TRANSISTORS 150                                                                                                                                                                                                                                                                                                                                                                                                                                    |

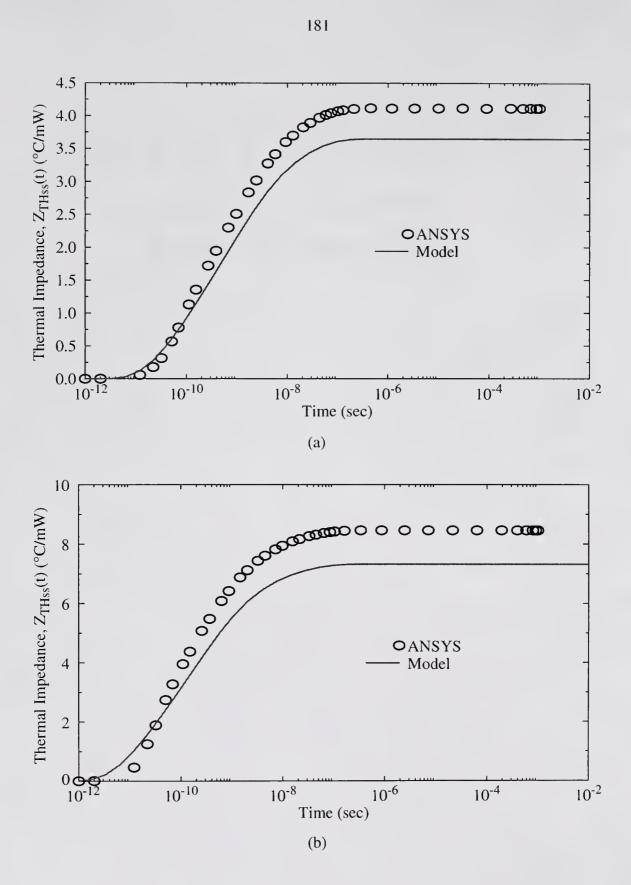

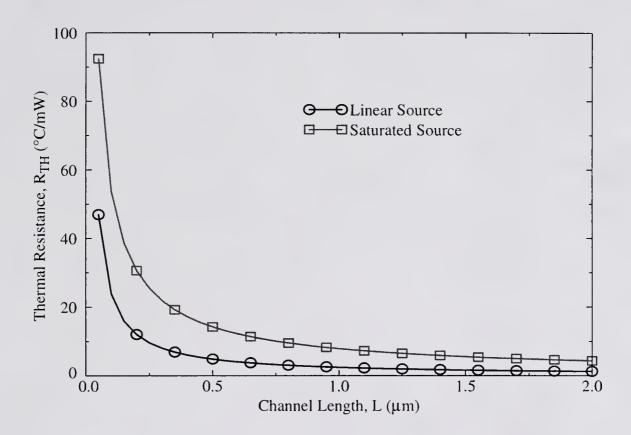

|   | 5.1 Introduction1505.2 Derivation of the Bulk MOSFET Thermal Impedance Model1535.2.1 The Linear Source Thermal Impedance1615.2.2 The Saturated Source Thermal Impedance1645.2.3 Effects of the Device Interconnects on the Thermal Impedance1655.2.4 Effects of Isolation Structures on the Thermal Impedance1715.3 Verification of the Bulk MOSFET Thermal Impedance Model1765.4 Summary182                                                                                                                                                   |

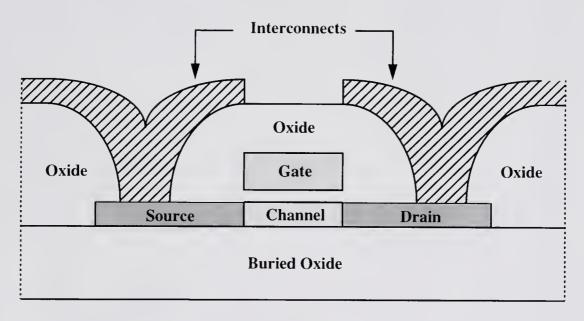

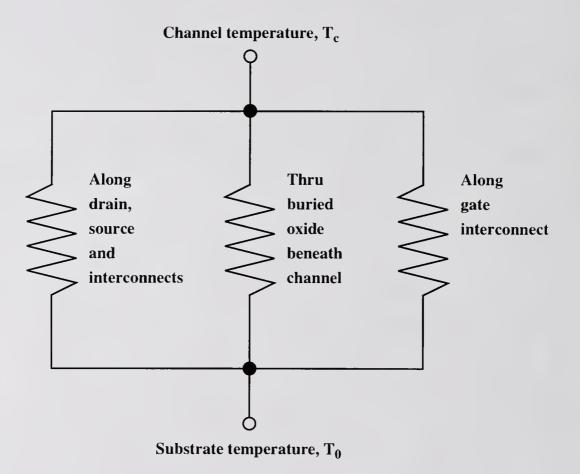

| 6 | A QUASI-THREE-DIMENSIONAL THERMAL IMPEDANCE MODEL FOR SILICON-ON-INSULATOR METAL-OXIDE-SEMICONDUCTOR FIELD-EFFECT TRANSISTORS                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 6.1 Introduction1846.2 Derivation of the SOI MOSFET Thermal Resistance Model1876.3 Verification of the SOI MOSFET Thermal Resistance Model2026.4 Derivation of the SOI MOSFET Thermal Impedance Model2046.5 Verification of the SOI MOSFET Thermal Impedance Model2126.6 Summary216                                                                                                                                                                                                                                                            |

| 7 | THE THERMAL IMPEDANCE PRE-PROCESSOR: TIPP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       | 7.1 Introduction                                                    | . 219 |

|-------|---------------------------------------------------------------------|-------|

|       | 7.2 A Description of TIPP                                           |       |

|       | 7.3 Generation of Thermal Equivalent Circuits                       |       |

|       | 7.3.1 Approximation of the Thermal Equivalent Poles/Time Constants. |       |

|       | 7.3.2 Calculation of the Thermal Equivalent Components              |       |

|       | 7.4 The Interface Between TIPP and Circuit Simulators               |       |

|       | 7.5 Summary                                                         | . 234 |

| 8     | CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WORK                     | . 238 |

|       | 8.1 Conclusions                                                     | . 238 |

|       | 8.2 Recommendations for Future Work                                 |       |

|       | 8.2.1 The Temperature Dependence of the Thermal Conductivity        |       |

|       | 8.2.2 Models for Thermal Effects Due to Advanced Isolation          | . 242 |

|       | 8.2.3 A Model for Thermal Coupling in SOI MOSFET Circuits           | . 243 |

| REFE  | RENCES                                                              | . 247 |

| RIOGI | PADHICAL SVETCH                                                     | 257   |

Abstract of Dissertation Presented to the Graduate School of the University of Florida in Partial Fulfillment of the

Requirements for the Degree of Doctor of Philosophy

PHYSICS-BASED THERMAL IMPEDANCE MODELS FOR THE SIMULATION OF SELF-HEATING IN SEMICONDUCTOR DEVICES AND CIRCUITS

By

Jonathan Scott Brodsky

August 1997

Chairman: Robert M. Fox

Major Department: Electrical and Computer Engineering

Inherent in the operation of semiconductor devices is self-heating, an

increase in operating temperature due to a device's own power dissipation. The

magnitude of the self-heating effect can be quantified by the value of the thermal

impedance, which describes the dynamic response of the device temperature to

variations in device power. The thermal impedance is determined primarily by

material properties and device structure. The implication of the self-heating effect is

that the change in temperature can alter the operating characteristics of a device,

which in turn, can affect circuit performance.

The primary focus of this dissertation is the development of physics-based

models for the thermal impedances of semiconductor devices. Models for the thermal

impedances of bipolar and field-effect transistors, on both bulk and silicon-on-

viii

insulator (SOI) substrates, are presented. All of the thermal impedance models were derived from the time-dependent heat conduction equation, resulting in compact analytic expressions for the thermal impedances. The physical nature of the thermal impedance models allows them to scale with the device structure and material properties, and they successfully reproduce results from both measurements and three-dimensional finite-element simulations. A circuit model for thermal coupling between transistors in a common substrate is also presented. The coupling model was used in conjunction with the bulk bipolar thermal impedance model to extract a lumped electrothermal model for multiple-emitter bipolar transistors.

The secondary objective of this work is the provision of an approach for incorporating these models into circuit simulators. It has been shown that the thermal impedance models can be represented by thermal equivalent circuits made up of resistors and capacitors, making them suitable for efficient circuit simulation. The computer program TIPP (Thermal Impedance Pre-Processor) is introduced. TIPP was developed to provide circuit simulators with convenient algorithms for generating thermal equivalent circuits. TIPP can calculate the component values for thermal equivalent circuits from either physical models or measured data, and is easily modified to interface with different circuit simulators.

#### CHAPTER I INTRODUCTION

#### 1.1 Self-Heating Effects in Semiconductor Devices

The physical properties of the materials used to fabricate semiconductor transistors depend on temperature. Therefore, the operating characteristics of a transistor (e.g. electrical currents and potentials), which are determined by the material properties, are also temperature dependent. The temperature at which a transistor operates is determined by the temperature of the surrounding environment (referred to as the "local ambient temperature") and the power dissipated in the device (referred to as the "self-heating effect"). Therefore, the time-dependent temperature of a transistor can be expressed as

$$T(t) = T_{amb} + \int_{0}^{t} P(t')h_{TH}(t - t')dt', \qquad (1.1)$$

where  $h_{TH}$  is the thermal impulse response and P is the instantaneous power. The second term on the right-hand side of (1.1) represents the temperature rise in the device

$$\Delta T(t) = P \otimes h_{TH},$$

(1.2)

where  $\otimes$  is the convolution operator. The temperature rise can also be expressed in

the frequency domain as

$$\Delta T(t) = \pounds^{-1}[Z_{TH}(s) \cdot P(s)], \qquad (1.3)$$

where £ $^{-1}$  represents the inverse Laplace transform and  $Z_{TH}(s)$  is the thermal impedance. The thermal impedance of a transistor describes the dynamic response of the device temperature to variations in device power, and is determined primarily by the material properties and the structure of the device. The transient thermal impedance can be defined as

$$Z_{TH}(t) = \pounds^{-1} \left[ \frac{1}{s} Z_{TH}(s) \right], \tag{1.4}$$

which represents the normalized thermal step response.

Since the power dissipation in (1.1) is determined by the operating characteristics of a transistor, it depends on temperature such that

$$P = P(T) = I_{dev}(T) \cdot V_{dev}(T), \qquad (1.5)$$

where  $I_{dev}(T)$  and  $V_{dev}(T)$  represent general currents and potentials within a given device, respectively. Consequently, there is feedback between the thermal and electrical operation of the device. Whereas the transistor temperature is usually assumed to be constant, the electrothermal coupling implied by (1.1) and (1.5) shows that the temperature actually varies with the device operation. Thus, to fully characterize the operation of semiconductor transistors, both the electrical and thermal behavior should be determined.

#### 1.1.1 Bipolar Transistors

In the forward-active mode, the operating characteristics of bipolar junction and heterojunction transistors (BJT's and HBT's) are controlled by the injection and diffusion of minority carriers in the base region. For an npn transistor, electrons are injected across the forward-biased base/emitter junction, causing an exponential increase in the minority carriers in the base. The electrons diffuse across the base and are swept into the collector by the reversed-biased base/collector junction. For a fixed base/emitter voltage, assuming negligible recombination in the quasi-neutral base, the collector current can be expressed as

$$I_{\rm C}(T) \propto n_{\rm i}^2(T) \cdot \exp\left(\frac{qV_{\rm BE}}{kT}\right),$$

(1.6)

where  $n_i$  is the intrinsic carrier concentration, q is the electron charge, k is Boltzman's constant and T is temperature. The overall temperature dependence of (1.6) is dominated by the relation between the intrinsic carrier concentration and temperature, given by

$$n_i^2(T) = N_c \cdot N_v \cdot exp(\frac{-E_g}{kT}),$$

(1.7)

where  $E_g$  is the semiconductor band-gap energy and  $N_c$  and  $N_v$  are the effective density of states in the conduction and valence bands, respectively. The junction voltage is always less than the band-gap and therefore, an increase in temperature causes an exponential increase of minority carriers in the base, resulting in an increase in collector current. Since the collector current is a significant component

of the power dissipation in a BJT, self-heating results in a regenerative feedback between the collector current and the temperature of the device. This positive feedback can lead to the destructive phenomenon of thermal runaway in BJT's [Shu90].

For fixed base current, the collector current can be expressed as

$$I_{C}(T) = \beta(T) \cdot I_{B}, \qquad (1.8)$$

where  $\beta(T)$  is the common-emitter current gain. For moderate injection levels, the current gain can be approximated by the ratio of the electrons injected into the base to the holes back-injected from the base to the emitter. This ratio, and hence  $\beta(T)$ , are typically high since the emitter usually has a higher doping level than the base. Due to heavy-doping effects in the emitter, the emitter band-gap is typically less than that in the base so that

$$\beta(T) \propto \frac{N_{DE}}{N_{AB}} \exp\left(\frac{-\Delta E_g}{kT}\right),$$

(1.9)

where  $\Delta E_g$  is the band-gap difference between the emitter and base, and  $N_{DE}$  and  $N_{AB}$  are the doping concentrations in the emitter and base, respectively. As shown by (1.9), the current gain is greater at higher temperatures; consequently, the collector current is, again, an increasing function of temperature. The rate of increase with temperature in this case, however, is not as significant as that for a device biased with a fixed base voltage. Therefore, the self-heating effect is not as substantial in BJT's driven by a fixed base current.

HBT's are bipolar devices that use band-gap engineering in either the emitter or base region to improve the current gain over homojunction BJT's. The resulting band-gap in the emitter is wider than that in the base, so that the potential barrier induced by the band-gap discontinuity effectively impedes the injection of carriers from the base to the emitter. When biased with a fixed base voltage, the temperature dependence of an HBT is similar to that of a standard BJT. However, when an HBT is driven with a fixed base current, the temperature dependence of the collector current is quite different than that of a BJT. While the collector current in this case can still be determined from (1.8), the common-emitter current gain is now expressed as

$$\beta(T) \propto \frac{N_{\rm DE}}{N_{\Delta B}} \exp\left(\frac{\Delta E_g}{kT}\right).$$

(1.10)

As a result of the band-gap being wider in the emitter than in the base, the sign of the exponential argument is now positive. Therefore, as opposed to a standard BJT, the current gain and the collector current decrease with increasing temperature. As a result, self-heating in HBT's can lead to the non-catastrophic failure mechanism known as current collapse [Sei93].

To reduce the effects of parasitic resistances and current-crowding, large bipolar devices are commonly fabricated using multiple devices connected in parallel [Shu90]. Multiple-emitter devices, both BJT's and HBT's, are capable of operating at high frequencies under high power densities [Win67, Mar93, Liu95b]. However, multiple-emitter devices suffer from more complex self-heating effects due to the thermal interactions among neighboring devices. The thermal coupling leads to

lateral temperature gradients across the device, resulting in the inner emitters operating at higher temperatures. Due to the positive feedback between junction temperature and junction current, the inner devices carry more current than those at the outer extremes. As the current density in the inner emitters increases, the self-heating effect in these devices accelerates. The premature activation of thermal runaway in BJT's and current collapse in HBT's is attributed to this thermal instability inherent in multiple-emitter devices [Win67, Liu93, Kag94, Lio94, Lio96].

#### 1.1.2 Field-Effect Transistors

For Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET's) operating in strong inversion, the current characteristics are determined by the drift current of carriers in the inverted channel region. For small drain voltages, a MOSFET operates in the linear region where the carrier velocity depends on the longitudinal electric field in the channel. In the linear region, the drain current can be approximated as

$$I_{D}(T) \propto \mu(T) \cdot \left(V_{GS} - V_{t}(T) - \frac{V_{DS}}{2}\right) V_{DS},$$

(1.11)

where  $\mu(T)$  is the carrier mobility,  $V_t(T)$  is the threshold voltage, and  $V_{GS}$  and  $V_{DS}$  are the applied voltages between the gate and source and drain and source, respectively. At higher drain voltages, the electric field at the drain end of the channel is large enough to cause the carrier velocity to saturate. In the saturation

region, the drain current can be expressed as

$$I_{D}(T) \propto Q_{c}(V_{GS}, V_{DS}, \mu(T)) \cdot v_{sat}(T), \qquad (1.12)$$

where  $Q_c$  is the channel charge and  $v_{sat}(T)$  is the saturated carrier velocity.

The overall temperature dependences of (1.11) and (1.12) are dominated by the sensitivity of the carrier mobility to changes in temperature. Due to increased lattice scattering at higher temperatures, mobility decreases as temperature increases. The reduction in mobility leads to a decrease in drain current, which implies that the drain current of a MOSFET is a decreasing function of temperature. At high power dissipation levels, the self-heating effect can cause the drain current to drop below the ambient temperature value. In such cases, the output conductance becomes negative, and the device exhibits a negative dynamic resistance (NDR) [Sha83].

MOSFET's fabricated on silicon-on-insulator (SOI) substrates have temperature dependences that are similar to those of their bulk counterparts, though the effects of self-heating can be enhanced due to the low thermal conductivity of the insulating layers. For non-fully depleted (NFD) SOI MOSFET's, however, floating-body effects further complicate the thermal effects [Wor97]. Impact-ionization-induced floating-body effects are known to cause the kink, or increase in drain current, in NFD SOI MOSFET's. The kink is affected by self-heating in two ways. First, at elevated temperatures, the onset of the impact-ionization is retarded. Second, an increase in recombination in the quasi-neutral body reduces the threshold-voltage shift caused by the impact-ionization. Therefore, in addition to a reduction in drain current due to mobility effects, self-heating also reduces the

current in NFD SOI MOSFET's through temperature-dependent floating-body effects.

#### 1.2 Self-Heating Effects in Semiconductor Circuits

Since the operating characteristics of transistors are affected by temperature, the integrated circuits that depend on these transistors will also be affected by changes in temperature. In modern digital circuits, the high switching speeds of the transistors, the relatively slow time constants associated with the temperature response and the low static power dissipation, all help reduce the instantaneous temperature rise. Consequently, self-heating effects are typically negligible in digital circuits. On the other hand, analog circuit applications commonly have significant power dissipation and can operate at frequencies which are comparable to the thermal time-constants. Therefore, analog circuits are generally more prone to self-heating effects.

### 1.2.1 Small-Signal Circuit Performance

The effect of self-heating on small-signal BJT characteristics was derived by Mueller and investigated in bipolar circuits by Fox et al. [Mue64, Fox93b]. The two-port small-signal admittance parameters, in the presence of self-heating, were shown to be

$$y_{mn} = \frac{y_{mnE} + D_m Z_{TH} I_m I_n}{1 - D_m Z_{TH} P}$$

(1.13)

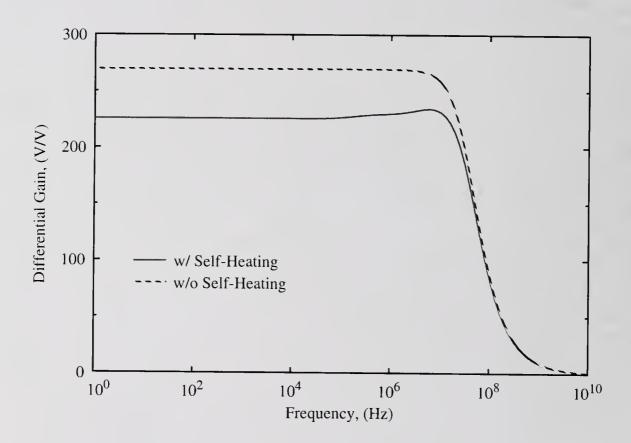

where y<sub>mnE</sub> are the admittance parameters neglecting self-heating, and D<sub>m</sub> represents the variation of the current I<sub>m</sub> with temperature. The denominator of (1.13) establishes the sensitivity of the admittance parameters to power, and has a significant impact as D<sub>m</sub>Z<sub>TH</sub>P approaches unity. The effect of the denominator generally becomes important only at high power dissipation. However, as the thermal impedance increases (i.e. due to device scaling), the power level that defines the threshold for self-heating effects will decrease. The second term in the numerator of (1.13) shows that the effect of self-heating on the admittance parameters is also proportional to the operating currents. For y<sub>11</sub> and y<sub>21</sub> the self-heating term in the numerator is small so that  $y_{11} \cong y_{11E}$  and  $y_{21} \cong y_{21E}$ . However, the effect of selfheating can be substantial in the numerators of y<sub>12</sub> and y<sub>22</sub>, even at moderate current levels. The thermal effects on these parameters can result in a coupling between the collector output admittance and the impedance of the base-driving source. Also, as shown in Figure 1.1, there can be a significant reduction in the voltage gain of BJT amplifiers.

The small-signal performance of analog MOSFET circuits can also be affected by self-heating. For moderate power levels, the thermal effects are similar to those in bipolar circuits. However, as mentioned previously, the drain current of a MOSFET decreases with increasing temperature, and significant self-heating can induce NDR. The effect of a negative output conductance can be investigated by examining the voltage gain of a MOSFET amplifier. As shown by Fox and Brodsky [Fox93a], if the devices in the amplifier enter a region of negative output conductance, the gain of the amplifier changes polarity. For an inverting amplifier,

Figure 1.1 The effect of self-heating on the small-signal gain of a BJT differential amplifier. The data was simulated using a version of SPICE, which was modified to account for dynamic variations in temperature [Zwe97], and the thermal impedance model for bipolar transistors presented in Chapter Two.

self-heating effects can therefore cause the gain to become non-inverting, resulting in hysteresis in the amplifier's output characteristics.

#### 1.2.2 Large-Signal Circuit Performance

The effects of self-heating on the large-signal operation of analog bipolar circuits was investigated by Fox et al. [Fox93b]. The types of circuits that are sensitive to thermal effects are typically those that depend on the precise control of BJT characteristics. For example, the mismatch in the reference and output currents of a current mirror can be increased due to self-heating-induced differences in the operating conditions of the transistors. Translinear circuits and band-gap voltage references can also be affected by self-heating due to their strong dependence on the thermal voltage. Thus, neglecting self-heating can result in significant discrepancies between the ideal and actual operation of these types of circuits. The large-signal transient operation of analog circuits is also affected by self-heating. The long time constants of the thermal characteristics can effectively slow down the electrical response of a circuit. Fox et al. showed that the five-percent settling time of a Gilbert multiplier increased by over an order of magnitude due to self-heating [Fox93b]. While the errors caused by self-heating can be reduced by careful circuit design, they can not be completely eliminated.

#### 1.3 Self-Heating Effects in Parameter Extraction

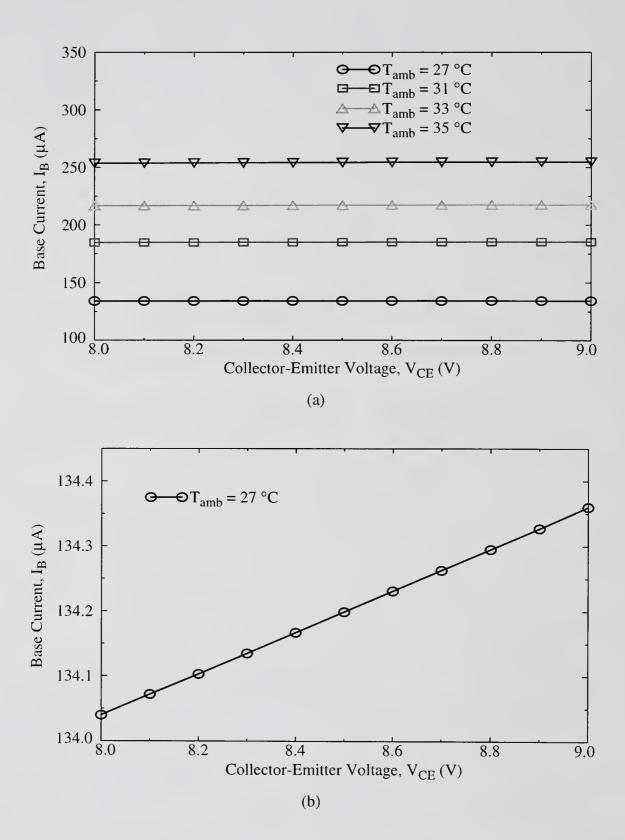

The extractions necessary to determine the behavioral characteristics of a semiconductor transistor are often performed at bias levels that cause moderate- to high-power dissipation. Typically, the parameters that are extracted are assumed to correspond to the ambient temperature at which the measurements are carried out. However, at significant power levels, self-heating will cause a temperature rise in the device. Neglecting the temperature rise that can occur during the measurements can lead to erroneous results [Zwe97]. For example, the Early voltage,  $V_A$ , of a BJT is commonly extracted from the slope of the  $I_C$ - $V_{CE}$  characteristics in the linear region of operation. If self-heating is significant, the slope of the output curves depends on the source that is driving the base [Fox93b]. Therefore, the exact meaning of the value extracted for  $V_A$  would be ambiguous unless the thermal effects were taken into account.

Various methods have been proposed for removing the effects of self-heating from parameter extraction. One approach augments a standard extraction routine with measurements designed to determine the thermal characteristics of the device. The full set of parameters can then be input to a global optimization routine to generate electrical-only parameters that are independent of self-heating [Zwe97]. Other techniques attempt to directly remove the effects of self-heating from the parameter extraction measurements by making the temperature rise in the given device negligible. The temperature rise can be minimized by performing the extractions in low-power regions, or by using complex high-speed measurements [Tu94, Jen95]. Since the device is not allowed to heat, the resulting device parameter

set would be approximately devoid of self-heating effects, and would essentially correspond to the given device operating under isothermal conditions. Consequently, the resulting electrical parameters would only pertain to device operation for low-power or high-speed circuit applications, and would not convey the proper device characteristics for applications that experience substantial self-heating effects. Thus, for a set of electrical-only parameters to correctly represent the characteristics of a device, over a wide range of operating conditions and biases, it should be augmented by additional parameters that describe the thermal attributes of the device.

#### 1.4 The Simulation of Self-Heating Effects

As shown in the previous sections, the operating characteristics of both individual transistors and circuits depend on temperature. Due to self-heating, the effective operating temperature depends on power dissipation and can therefore vary under different operating conditions.

By solving the time-dependent heat conduction equation and energy balance equations for electrons and holes, numerical device simulators can model phenomena associated with dynamic self-heating in individual transistors [Lia94]. While this approach is invaluable for examining the detailed physics that govern the operation of semiconductor devices, it is impractical for simulating all but the simplest of circuits. Therefore, to investigate the effects of dynamic self-heating on a broad range of circuits, a more efficient simulation approach is necessary.

The standard version of most circuit simulators such as Berkeley SPICE [Nag75] and HSPICE [Hsp92], treat temperature as a static global parameter. This has two significant implications. All of the semiconductor devices in a simulation operate at the same temperature, and that temperature remains constant throughout the simulation. Due to these constraints, a circuit simulator may not accurately represent the physical operation of a circuit, where spatial and temporal variations of the temperature can cause each device to operate at its own local temperature. To account for the temperature dependence of a circuit's operation, circuit simulators should be capable of independently tracking the dynamic temperature of each device in the circuit.

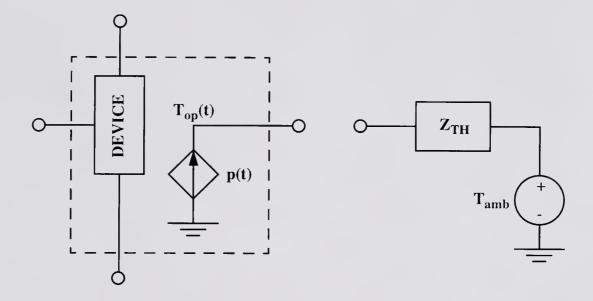

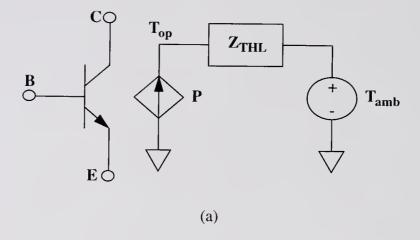

A common approach for creating an electrothermal circuit simulator (ETCS) uses the concept of the thermal impedance and the analogy between electrodynamics and heat flow to account for dynamic temperature variations. This approach allows temperature to be represented as an electrical potential and power as an electrical current [Lee96, Zwe97]; therefore, the local operating temperature of a device can be thought of as simply another "bias" condition. To facilitate the temperature "bias" condition, an external node is added to a given compact device model [McA92, Fos95, Lee96, Zwe97]; such a configuration is shown in Figure 1.2. Attached to this node, internal to the device model, is a controlled current source that represents the instantaneous power dissipation. The parameter set for the device model should be modified to include the correct temperature dependences. When the modified device model is used for a circuit simulation, a thermal impedance (and, in some case, a voltage source to represent the reference ambient temperature) can be

Figure 1.2 A generalized schematic showing a common method for modifying a compact device model to include temperature as a variable. The dashed box outlines the new model with the added temperature node; DEVICE represents the original electrical-only model.

attached to the new external node. Therefore, the voltage generated at this additional node represents the local temperature of the device. The electrical-only device model is first solved at the ambient temperature; this solution results in an initial guess for the device power dissipation. This power is then used to calculate the temperature rise in the device. Once the approximate local operating temperature is calculated, it is used to update the temperature-dependent model parameters, which are used to recalculate the electrical bias potentials and currents of the device model. This procedure is repeated until self-consistent solutions for the temperature and electrical biases are reached. Thus, an effective operating temperature can be independently calculated for each device in a simulation, and that temperature can now vary with the operating point.

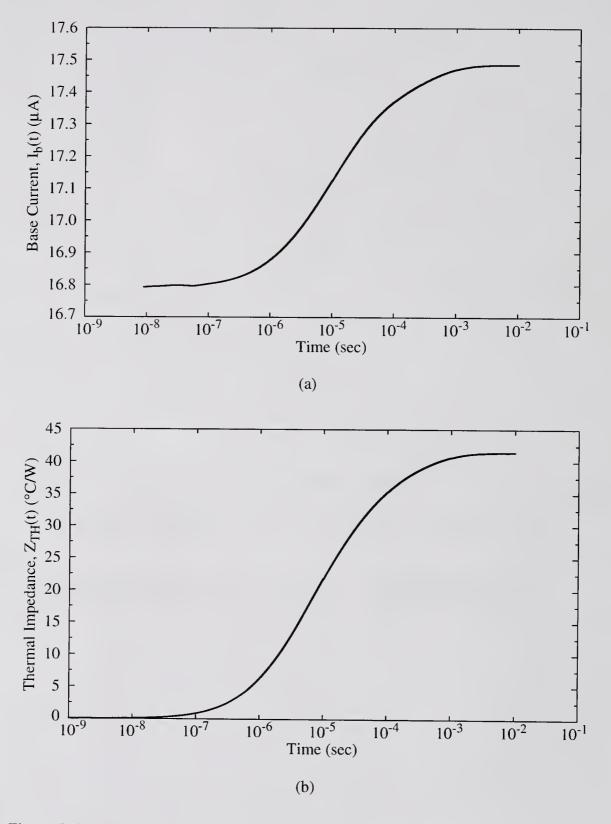

#### 1.5 Thermal Equivalent Circuits

The data that quantify the thermal impedance of a transistor are typically in the form of discrete data points for the temperature rise, normalized to a unit-step increase in power dissipation, versus time or frequency. In such a format, the thermal impedance data are not readily accessible by an ETCS. While data in a tabular format can be used without much complexity for DC and AC simulations, an inefficient convolution computation would be required to use the data for transient simulations. Therefore, a representation for the thermal impedance is needed that both accurately models the physical data and can be easily incorporated into an ETCS for efficient DC, AC and transient simulations.

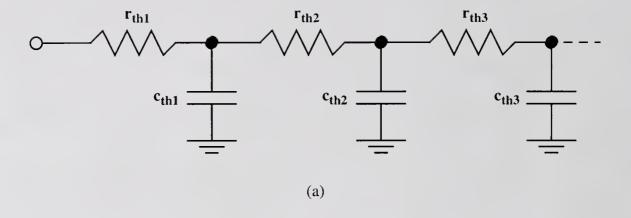

In an ETCS, when a current representing the power dissipation in a transistor is applied to the thermal impedance, Z<sub>TH</sub>, the resulting voltage represents the temperature rise in that transistor. By invoking the analogy between electrodynamics and heat flow, the thermal impedance can be represented as an electrical impedance. Common representations for the electrical impedance circuits are shown in Figure 1.3. The resistances and capacitances that comprise the impedance effectively represent the lumped three-dimensional thermal resistance and heat capacity of the semiconductor device structure. Therefore, the overall electrical network can be referred to as a thermal equivalent circuit. The values for the individual elements of a thermal equivalent circuit can easily be determined by numerically fitting the circuit to existing thermal impedance data. Thermal equivalent circuits are directly applicable for DC and AC electrothermal simulations since, in such cases, the voltage drop across the network is simply equal to the product of the current and the network resistance or impedance. In addition, such networks inherently provide an efficient method for effecting the necessary transient convolution.

As will be shown in the subsequent chapters of this dissertation, the fundamental nature of heat flow is that of a distributed system. The dynamic temperature rise in a device due to self-heating can occur over three or more decades of time or frequency. A single time constant associated with a simple exponential function can not represent the distributed behavior of self-heating. Consequently, the network response of the single-pole thermal equivalent circuits which have been proposed in previous works [McA92, Bau93, Lee93, Tu94], will not accurately

Figure 1.3 Thermal equivalent circuits used to represent a thermal impedance for circuit simulation: a) Cauer network representation; b) Foster network representation.

model the dynamic thermal impedance. Thermal equivalent circuits consisting of cascaded resistor/capacitor stages, as exemplified in Figure 1.3, effectively provide a distributed network response, and therefore allow a more accurate representation of a dynamic thermal impedance [Bro93].

In the work by Szekely and Van Bien [Sze88], the Foster circuit (Figure 1.3b) was shown to be an invalid representation of a discretized thermal network. This point is valid in the context of numerical simulations (e.g. finite difference or finite element) where the transistor structure is modeled by a distributed thermal network. In that case, the node-to-node capacitances of the Foster network do not have physical meaning and the Cauer network would be the proper physical discretization of the given thermal domain. However, in this dissertation, the thermal equivalent circuit is simply a numerical representation of a thermal impedance, and the validity of its format is moot. Yet, for the purpose of representing a lumped thermal impedance in an ETCS, the Foster network form offers an important advantage over the Cauer form: the time constants associated with a given Foster network are independent of any surrounding circuit elements. This characteristic is beneficial when individual thermal equivalent circuits must be connected to model different components of a transistor structure or the thermal interactions between transistors. Therefore, the Foster network form will be assumed for any thermal equivalent circuits within this dissertation.

#### 1.6 The Need for Physics-Based Thermal Impedance Models

In the previous two sections, the concept of the thermal impedance is adopted to model the temperature rise in a transistor as a function of that device's power dissipation. For the purpose of circuit simulation, the thermal impedance can be represented by a network of resistances and capacitances that effectively represent the lumped thermal characteristics of a transistor. To successfully synthesize a thermal equivalent circuit, tangible data for the thermal impedance are necessary.

One approach to obtain the thermal impedance of a transistor is to extract it from measurements [Lee95, Zwe96]. While this empirical approach provides accurate temperature information, such measurements are somewhat difficult, for several reasons. To begin with, thermal measurements are very time-consuming. The extraction procedure is generally divided into two steps, the first of which dominates the total measurement time. This step is required to calibrate the relation between the temperature and the physical characteristic that is being used to monitor the temperature (e.g. the base current and drain current in bipolar and field-effect transistors, respectively). The calibration is performed at multiple ambient temperatures at DC and is thus limited by the long time constants associated with steady-state heat flow. To make such thermal measurements requires special measurement equipment such as a thermal wafer chuck or oven to accurately control the temperature of the devices being measured. Finally, the results of any such extraction are limited to the specific device being measured. Thus, the entire procedure would have to be repeated for each transistor structure and transistor type of interest.

Another approach, which avoids the inherent complexities of thermal measurements, is to derive the thermal impedance of a transistor from the physical equations that govern the temperature and heat flow in the device. Physical thermal modeling is desirable because it can give the temperature behavior as a function of the device structure and material properties alone; therefore, the effects of device technology scaling on the thermal impedance can be predicted. The requirements of accurate physical modeling (e.g. multi-dimensional numerical simulations) tend to conflict with the needs for simplicity and efficiency in circuit simulation. However, a thermal impedance model does not need to be absolutely accurate to provide reasonable results within an ETCS. Therefore, by using certain heuristic assumptions, compact physical models for the thermal impedance, suitable for efficient simulation, can be derived. It is important, though, that the correlation between the accuracy of the thermal impedance models and the accuracy of the simulated electrical characteristics of a semiconductor device in the presence of selfheating be understood.

The sensitivity of a given electrical parameter, X, of a semiconductor device to the thermal resistance can be defined as

$$S_X^{R_{TH}} \equiv \frac{R_{TH}}{X} \cdot \frac{\partial X}{\partial R_{TH}}.$$

(1.14)

As an example, since the output current of a device is very important for characterizing performance, (1.14) can be used to determine the sensitivity of the collector and drain currents of BJT's and MOSFET's, respectively. Using (1.1) in the steady-state limit and (1.6) with (1.14), the sensitivity of the collector current of a

BJT is expressed as

$$S_{I_{C}}^{R_{TH}} = \frac{q \cdot (V_{g} - V_{BE}) \cdot R_{TH} \cdot P}{k \cdot (R_{TH} \cdot P + T_{0})^{2}},$$

(1.15)

where  $V_g$  is the semiconductor band-gap voltage. A similar expression for the sensitivity of the drain current of a MOSFET can be determined using the current equation given by Fox and Brodsky [Fox93a], which results in

$$S_{I_D}^{R_{TH}} = -\alpha \cdot \left[ \frac{R_{TH} \cdot P}{T_0} + 1 \right]^{-1} \cdot \frac{R_{TH} \cdot P}{T_0},$$

(1.16)

where  $\alpha$  is typically between 1.5 and 1.8 (assuming that the temperature dependence of the drain current is dominated by the temperature sensitivity of the carrier mobility). The expected level of error in simulated output currents can be approximated by the product of the sensitivity and the anticipated error in the thermal impedance model. Therefore, as shown by (1.15) and (1.16), the relation between the accuracy of the thermal impedance models and the accuracy of the calculated electrical parameters depends on the power dissipation and the sensitivity of the electrical parameters to temperature. Consequently, the level of accuracy of a thermal impedance model is more critical for devices with electrical characteristics that are highly sensitive to temperature (e.g. BJT's as opposed to MOSFET's). At low power dissipation levels, where the temperature rise is small compared to the ambient temperature, the error in the thermal impedance model will not directly correspond to the error in the calculated operating temperature. For a temperature rise of twenty degrees, the sensitivities of the BJT collector current ( $V_{\rm BE}$  = 0.8) and

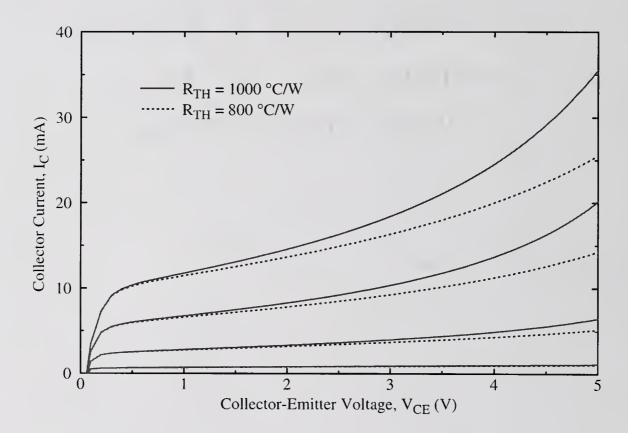

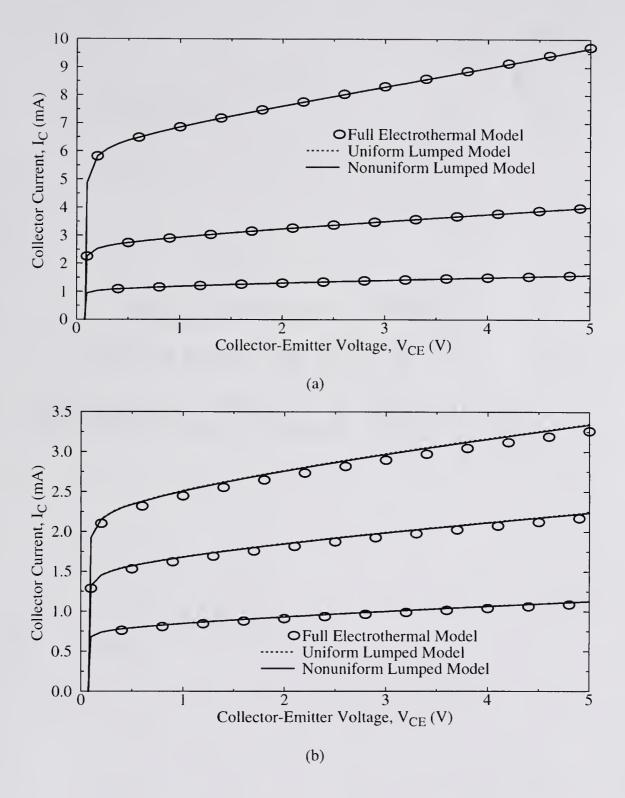

MOSFET drain current are 0.7 and -0.1, respectively. In such a case, the error in the electrical characteristics will tend to be lower than the error in the thermal impedance. Whereas at large power dissipation levels, the temperature rise can be much larger than the ambient temperature, and the error in the thermal impedance model will directly correspond to the error in the calculated operating temperature (for a temperature rise of one-hundred degrees, the respective BJT and MOSFET current sensitivities are 2 and -0.4); in which case, large errors in the calculated electrical characteristics can result. Figure 1.4 shows an example of BJT characteristics simulated assuming a 20% error in the thermal resistance model; the simulations were performed using the modified version of SPICE created by Lee [Lee96]. The data clearly shows that for larger temperature rises, the error in the calculated current (due to errors in the thermal impedance model) increases.

The motivation behind this dissertation is the development of compact thermal impedance models for semiconductor transistors. These models can provide a reasonably accurate representation of the dynamic temperature response within a device; more importantly, since the models depend mainly on the physical structure of a device, they can correctly anticipate the effects of technology scaling on the thermal behavior. Physics-based thermal impedance models allow an ETCS to predict dynamic self-heating effects in circuits and can also provide more accurate electrical parameter extraction. In addition, when the thermal impedance models are coupled with physics-based compact device models, the combination provides an efficient tool for studying self-heating in semiconductor transistors.

Figure 1.4 Simulated output characteristics of a BJT, assuming that  $R_{TH} = 1000~^{\circ}\text{C/W}$ , for  $V_{BE} = 0.80,~0.85,~0.90$  and 0.95 V. The simulations are repeated assuming a 20% error in the thermal resistance model, so that  $R_{TH} = 800~^{\circ}\text{C/W}$ .

#### 1.7 Organization

Chapter Two presents a physics-based model for the thermal impedance of bulk junction-isolated bipolar transistors. The model is derived by solving the three-dimensional time-dependent heat conduction equation in the substrate. The ability of the model to represent bulk BJT/HBT's with either LOCOS or trench isolation is investigated. To account for multiple-emitter bipolar transistors, the thermal impedance model is extended to represent multiple heat sources. The accuracy of the model is evaluated using measurements and three-dimensional finite-element simulations.

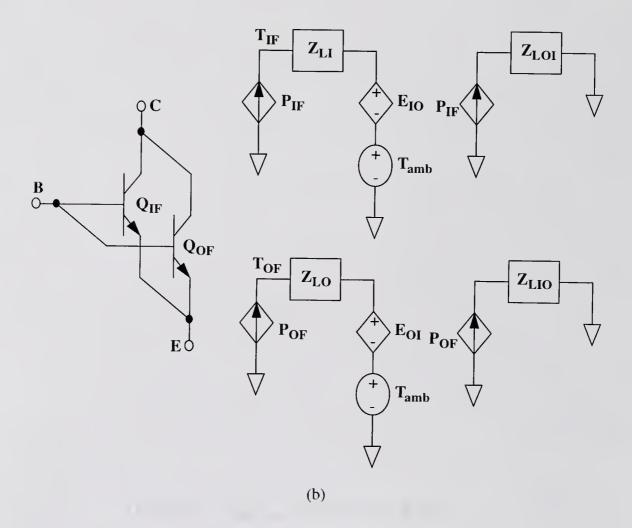

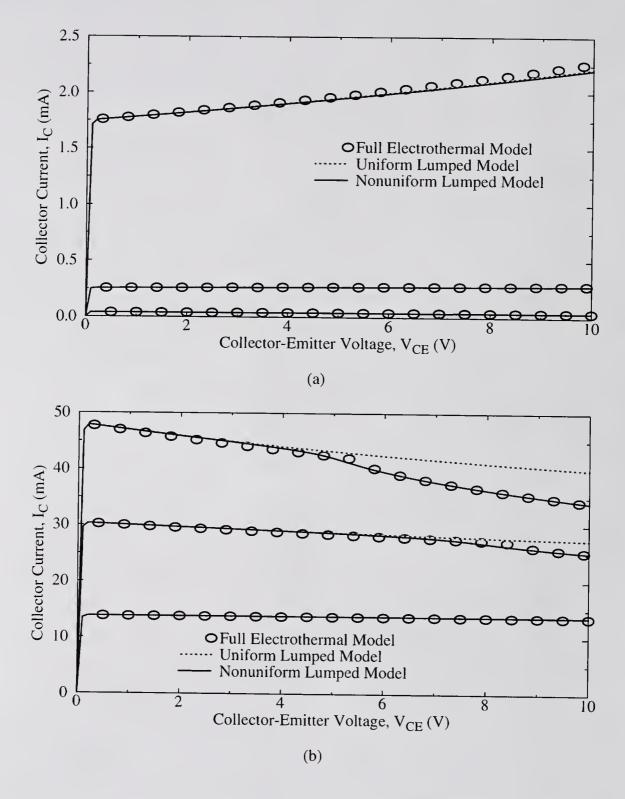

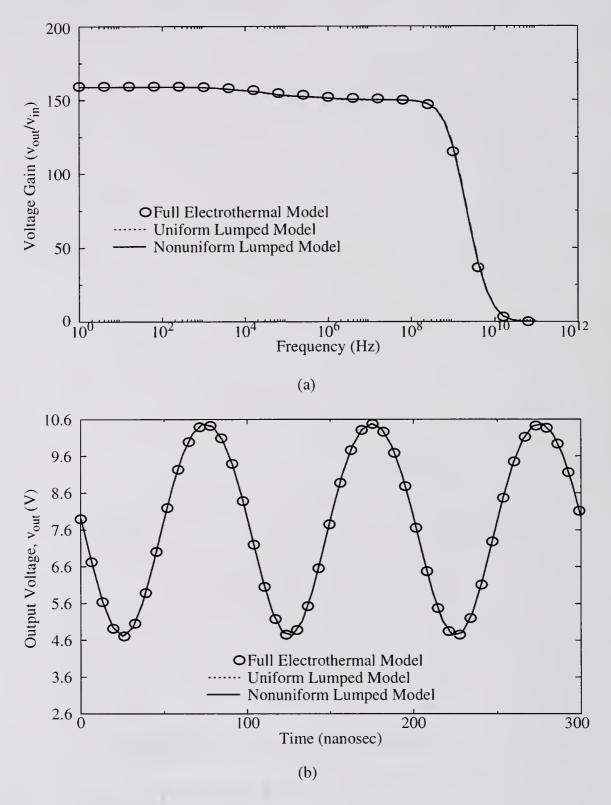

Chapter Three describes a circuit network for modeling thermal interactions between devices located in the same substrate. The network is developed for the specific application of multiple-emitter bipolar devices, but is shown to be valid for general cross-substrate thermal coupling in circuits. A method for improving the simulation efficiency of a multiple-emitter BJT/HBT electrothermal model, using a lumped thermal impedance model, is presented. The validity of the lumped modeling approach is supported with comparisons to the full electrothermal model.

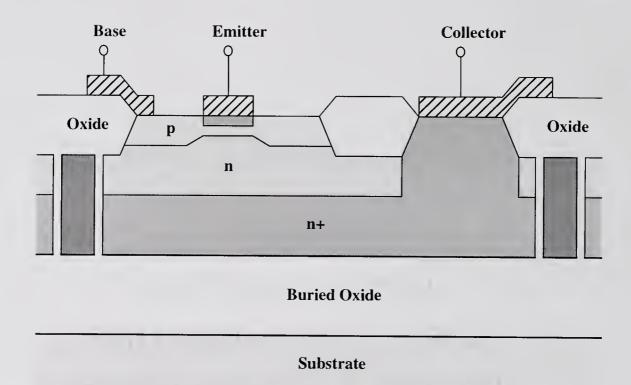

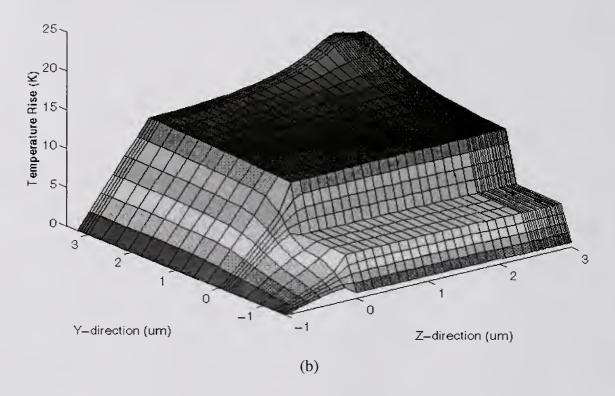

Chapter Four presents a predictive scalable model for the thermal impedance of BJT's with full dielectric isolation. The model is derived by solving the three-dimensional time-dependent heat conduction equation in the substrate accounting for the buried oxide and trench isolation. In the limit of steady-state heat conduction, the thermal impedance model is simplified, resulting in a closed-form

model of the thermal resistance. The accuracy of both models is evaluated using three-dimensional finite-element simulations and measurements.

Chapter Five describes a physics-based model for the thermal impedance of bulk MOSFET's. The model is derived by solving the three-dimensional time-dependent heat conduction equation in the substrate. The effects of the device interconnects and isolation structures, such as LOCOS and trenches, on the thermal impedance are investigated. The accuracy of the model is evaluated using measurements and three-dimensional finite-element simulations.

Chapter Six presents a predictive scalable model for the thermal impedance of SOI MOSFET's. The model is initially derived for steady-state heat conduction by coupling separate one-dimensional heat conduction analyses in the silicon film and interconnects. The derivation is then carried out for the case of time-dependent heat conduction, resulting in a model for the dynamic thermal impedance. The accuracy of both models is evaluated using three-dimensional finite-element simulations and measurements.

Chapter Seven describes a computer program developed to facilitate thermal modeling in circuit simulation. The program, referred to as the Thermal Impedance Pre-Processor (TIPP), functions as a framework for obtaining the component values of thermal equivalent circuits from the thermal impedance models presented in Chapters Two through Six.

Chapter Eight concludes the dissertation with a summary of the accomplishments of this work and suggestions for future modeling efforts.

# CHAPTER 2 A THREE-DIMENSIONAL THERMAL IMPEDANCE MODEL FOR JUNCTIONISOLATED BIPOLAR TRANSISTORS

#### 2.1 Introduction

The models derived in this chapter provide closed-form physical solutions for predicting the thermal impedances for single- and multiple-emitter bipolar junction (BJT) and heterojunction bipolar (HBT) transistors, based solely on device geometry and material properties. These models can predict both steady-state and dynamic self-heating due to the semiconductor substrate. Previous works in this area provided values for the thermal impedance of BJT's or HBT's, but were either limited by assumptions or relied on non-predictive measurement techniques. For example, the thermal impedance model derived by Fox and Lee [Fox91a] is limited to single-emitter devices. The analyses in other works only provide models for the steady-state thermal resistance [Lio93, Bau94, Daw94, Lio94, Lio96]. Some authors have used measurement techniques to extract either the steady-state thermal resistance or simple one-pole approximations for the thermal impedance [Bau93, Liu93, Daw94, Liu95a, Liu95b]; in either case, the results do not provide a complete picture of self-heating and are not predictive.

The thermal analysis by Joy and Schlig [Joy70] serves as the foundation for deriving of thermal impedance model, and the first part of this chapter re-

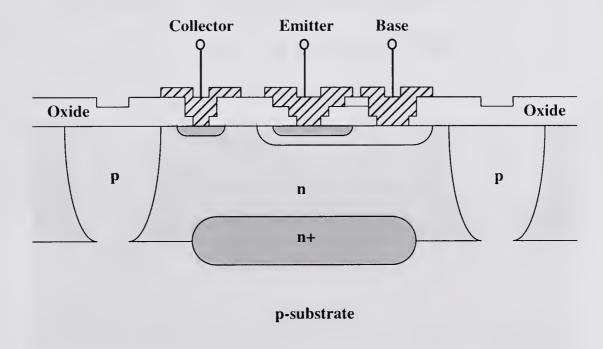

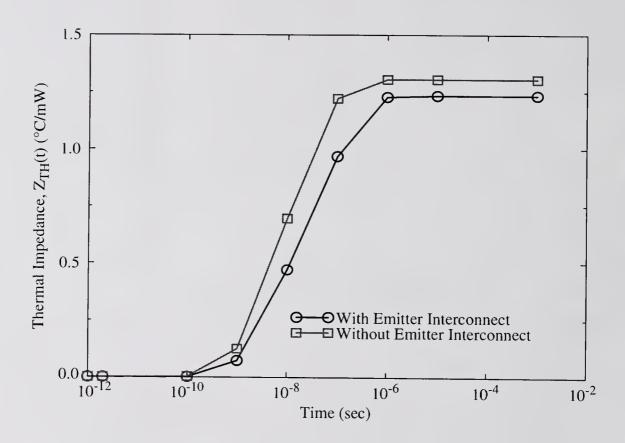

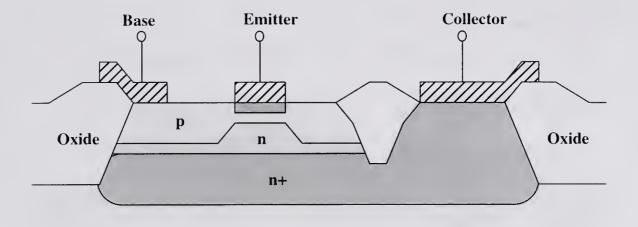

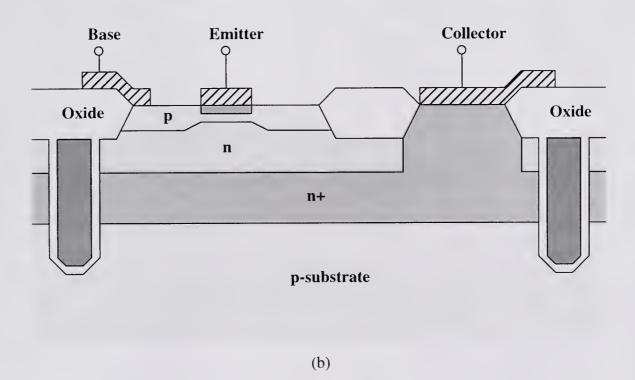

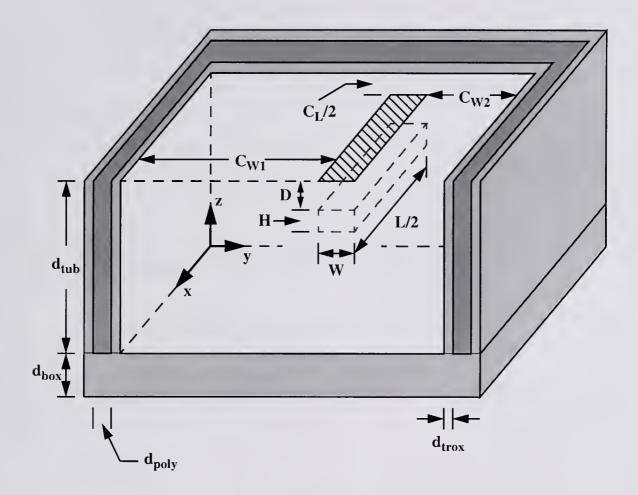

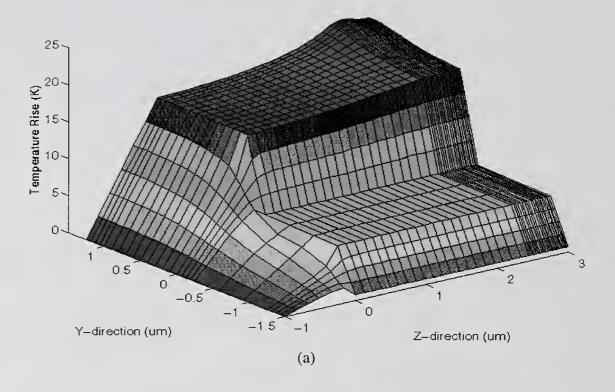

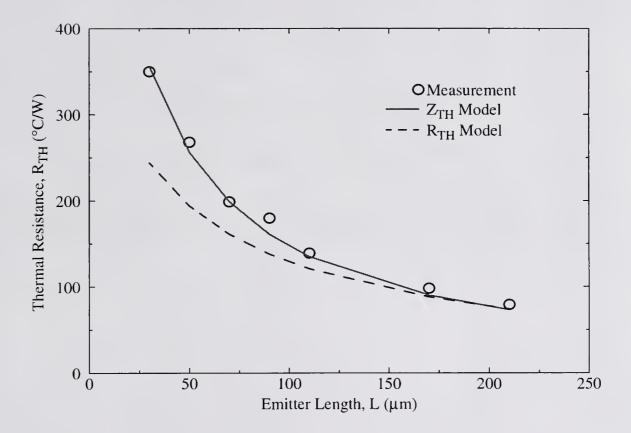

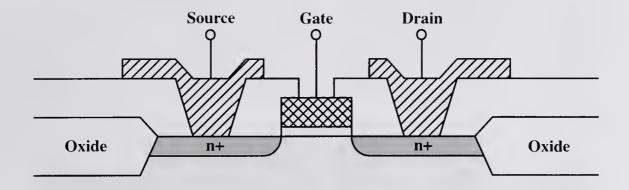

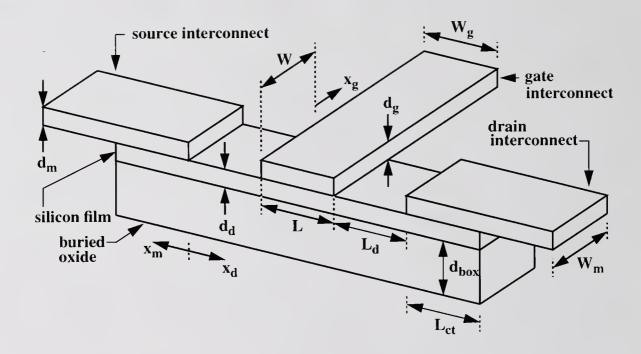

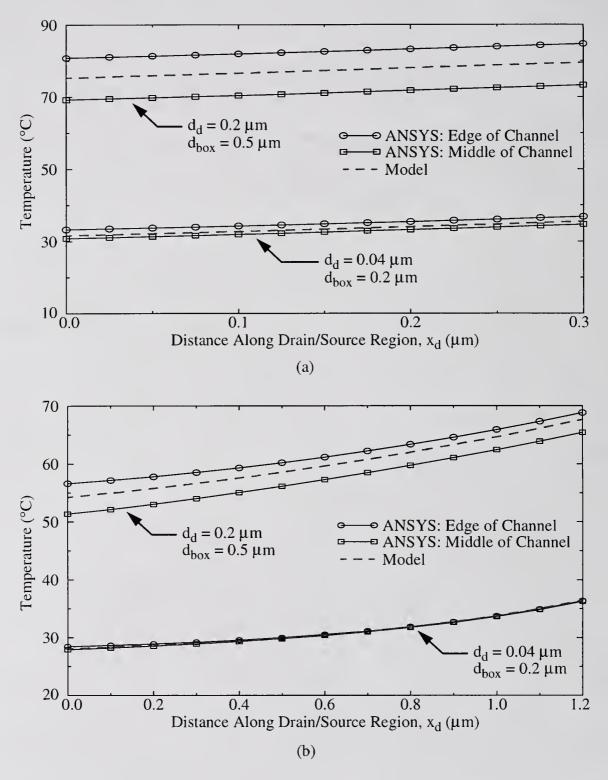

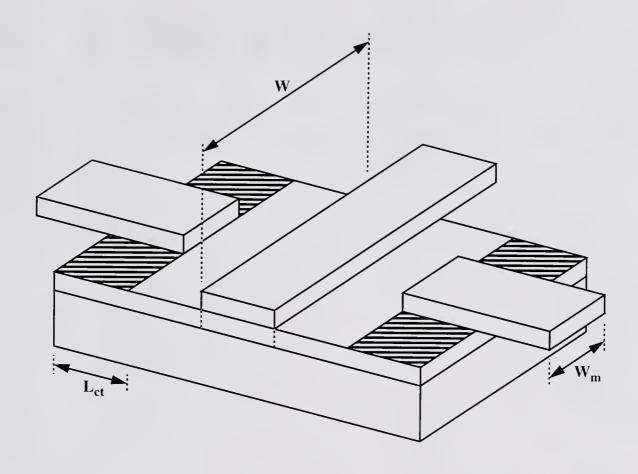

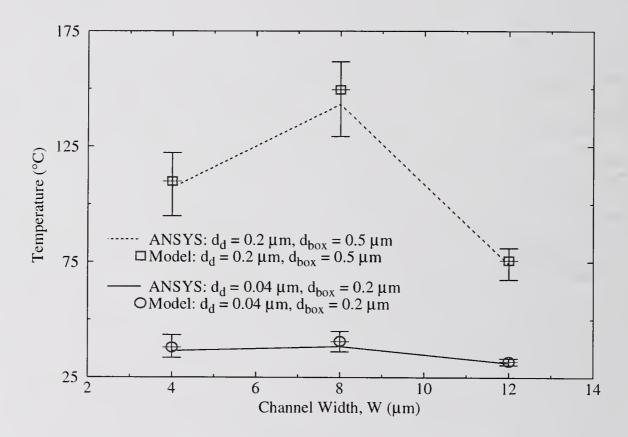

examines this work to provide a clear background for modifications made to the model later in the chapter. The thermal impedance model developed by Joy and Schlig was derived for single-emitter, junction-isolated BJT's operating in the forward-active region. A diagram of a typical junction-isolated npn BJT is shown in Figure 2.1. In this chapter, the basic model is modified to account for variations in substrate thickness. The effects of interconnect metallization and different isolation technologies on the thermal impedance, and thus on the performance of the model for advanced device structures, are investigated. The single-emitter thermal impedance model is finally extended to account for BJT/HBT's with multiple emitter fingers.

# 2.2 Derivation of the Single-Emitter BJT/HBT Thermal Impedance Model

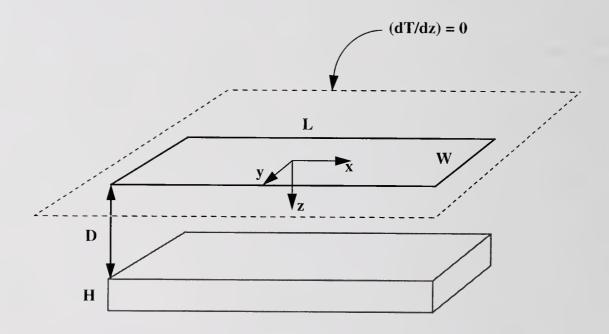

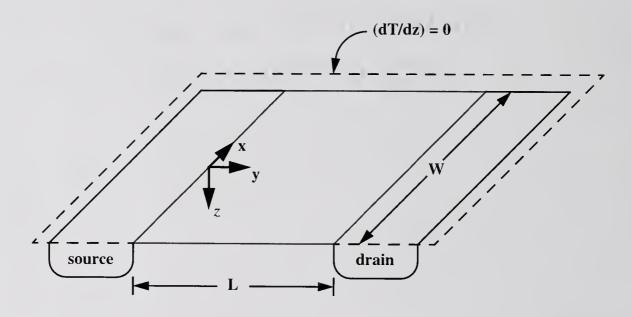

For the derivation of the single-emitter bulk BJT/HBT thermal impedance model, the semiconductor substrate is represented by a homogeneous semi-infinite half-space with an adiabatic top surface (no heat transfer perpendicular to the surface). The back side of the substrate is assumed to be held at a constant temperature, T<sub>0</sub>. Since the substrate material is assumed to be homogeneous, the model most directly applies to junction-isolated transistors. The effects of other types of isolation structures used in bulk technologies, such as recessed LOCOS (local oxidation of silicon) or back-filled trenches, on the thermal response are not taken into account. Figure 2.2 illustrates the simplified device geometry assumed for the model derivation; the diagram focuses on the "electrically active" portion of the device that lies directly beneath the emitter stripe, which has a width W and length

Figure 2.1 Cross-section of a typical junction-isolated bipolar junction transistor (BJT).

Figure 2.2 The simplified device geometry used to define the solution domain for the bulk, single-emitter BJT/HBT thermal impedance model. The substrate is represented by a semi-infinite half-space with an adiabatic surface (the dotted lines). The emitter stripe has a width W and length L. The heat source (the rectangular volume) is displaced a distance D below the surface of the device, equivalent to the depth of the base/collector junction. The heat source has a thickness H which approximates the base/collector space-charge region (SCR).

L. The imbedded heat source represents the base/collector space-charge region (SCR), which is further represented by a rectangular volume with a thickness, H. The heat generated in this region is assumed to be due to uniform power dissipation. This assumption is reasonable for devices in the forward-active region of operation prior to any high current effects, as the current distribution in the intrinsic device will be approximately uniform. The electric field gradient in the base/collector SCR can also be neglected since it does not greatly affect the thermal impedance model. The heat source is displaced beneath the surface of the substrate by a distance D, assumed to be the depth of the base/collector junction. Thus, any encroachment of the base/collector SCR into the base region is neglected (which is reasonable since the base typically has a higher doping than the collector).

Representing the substrate as a semi-infinite medium presumes that the back-side and the lateral edges do not influence the thermal response of the device. Neglecting the effects of the back side of the substrate on the thermal response is reasonable since a typical wafer is about 1000 times thicker than the heat source. Neglecting the effects of the lateral boundaries requires that the device be located sufficiently far from the substrate edges; the work by Fox et al. [Fox93b] suggests that this assumption is valid for any device that is at least a distance  $5\sqrt{W \cdot L}$  from any lateral edge. The surface of the substrate is assumed to be the only boundary that affects the thermal response of the device and it is considered to be adiabatic; thus, conduction through the interconnects and conduction/convection from the surface are neglected. Ignoring thermal energy transport from the substrate surface is supported by the work of Berger and Chai and Goodson et al. [Ber91, Goo95];

however, they were mainly concerned with transport via convection to a surrounding gas (namely air). Nonetheless, for the regions of the device covered by oxide, it is unclear whether there is substantial heat conduction to this overlying oxide. From the analysis of Goodson et al. [Goo95], the device-to-oxide thermal conductance is of the order of G = 4rk, which corresponds to an isothermal disk of radius r on the boundary of a semi-infinite medium of thermal conductivity k. Approximating the radius as  $\sqrt{(WL)/\pi}$  and using the room-temperature thermal conductivity of SiO<sub>2</sub>, the device-to-oxide thermal conductance for a typical device is on the order of 1 x 10<sup>-6</sup> (W/°C). Comparably, the device-to-substrate thermal conductance is on the order of 1 x 10<sup>-3</sup> (W/°C), showing that the majority of heat will flow through the substrate.

The temperature rise at any point within the device can be described by the nonhomogeneous three-dimensional heat conduction equation

$$\nabla^2 \Delta T(x, y, z, t) + \frac{g(x, y, z, t)}{k} = \frac{1}{\alpha} \frac{\partial \Delta T(x, y, z, t)}{\partial t}$$

(2.1)

and the boundary conditions

$$\Delta T(\pm \infty, y, z, t) = 0 \tag{2.2}$$

$$\Delta T(x, \pm \infty, z, t) = 0 \tag{2.3}$$

$$\left. \frac{\partial \Delta T(x, y, z, t)}{\partial z} \right|_{z = 0} = 0 \tag{2.4}$$

$$\Delta T(x, y, \infty, t) = 0, \qquad (2.5)$$

where  $\Delta T$  is the temperature rise above the local ambient ( $\Delta T = T - T_0$ ), g is the internal energy generation density, k is the thermal conductivity,  $\alpha$  is the thermal diffusivity ( $\alpha = k/(\rho \cdot c_p)$  where  $\rho$  is the density and  $c_p$  is the specific heat) and t is time. Typical values for the material properties are given in Table 2.1.

Table 2.1 Semiconductor material properties

| Parameter                                           | Si    | GaAs  |

|-----------------------------------------------------|-------|-------|

| k (W cm <sup>-1</sup> K <sup>-1</sup> )             | 1.412 | 0.455 |

| ρ (g cm <sup>-3</sup> )                             | 2.328 | 5.316 |

| c <sub>p</sub> (J g <sup>-1</sup> K <sup>-1</sup> ) | 0.70  | 0.35  |

Source: [Mul77]

Equation (2.1) assumes that the thermal conductivity is independent of temperature and position. Neglecting the temperature dependence of the thermal conductivity is reasonable for a moderate temperature rise, where the temperature rise will vary linearly with power dissipation. However, for large temperature excursions, the value of the thermal conductivity can vary significantly; the thermal conductivities of Si and GaAs will vary from their room-temperature values by more than 20% above 355 and 390 K, respectively [Gao89]. For such large temperature excursions, the linear relation between temperature rise and power will not be valid. However, the temperature dependence of the thermal conductivity can be accounted for by

using the Kirchoff transformation [Joy75], as discussed in Chapter Eight. Neglecting the spatial dependence of the thermal conductivity implies that the effect of dopant atoms is ignored. In the works by Weber and Gmelin and Goodson et al. [Web91, Goo95], the thermal conductivity of doped silicon (up to 1x10<sup>18</sup> and 1.7x10<sup>19</sup> dopant atoms cm<sup>-3</sup>) above 300 K is shown to differ only slightly from that of intrinsic silicon. Since the majority of the substrate is typically low-doped semiconductor material, neglecting the doping effects on the thermal conductivity is reasonable.

With the initial thermal conditions within the substrate specified as

$$\Delta T(x, y, z, 0) = 0,$$

(2.6)

the solution to (2.1) can be expressed in the form

$$\Delta T(x, y, z, t) = \frac{\alpha}{k} \int_{t'=0}^{t} dt' \int_{V} G(x, y, z, t | x', y', z', t') g(x', y', z', t') dv'$$

(2.7)

where

$$G(x, y, z, t | x', y', z', t') = \frac{1}{8[\pi\alpha(t - t')]^{3/2}} exp \left[ \frac{-(x - x')^2}{4\alpha(t - t')} \right] exp \left[ \frac{-(y - y')^2}{4\alpha(t - t')} \right]$$

$$\cdot \left\{ exp \left[ \frac{-(z - z')^2}{4\alpha(t - t')} \right] + exp \left[ \frac{-(z + z')^2}{4\alpha(t - t')} \right] \right\}$$

(2.8)

is the Green's function for the given boundary-value problem [Ozi93]. Equation (2.8) is the solution to

$$\nabla^2 G + \frac{g_p^i \cdot \delta(x - x')\delta(y - y')\delta(z - z')\delta(t - t')}{k} = \frac{1}{\alpha} \frac{\partial G}{\partial t}$$

(2.9)

for the boundary and initial conditions given by (2.2) through (2.6), and physically represents the temperature at point (x, y, z) at time t, due to an instantaneous point source,  $g_p^i$  (W s), of unit strength at point (x', y', z') at time t'.

To account for the heat-generation volume ( $V = W \cdot L \cdot H$ ), (2.8) is substituted into (2.7) and integrated over the base/collector SCR, resulting in

$$\Delta T(x, y, z, t) = \int_{t'=0}^{t} \frac{P(t')}{8\rho c V} \left[ erf\left(\frac{L/2 + x}{\sqrt{4\alpha(t - t')}}\right) + erf\left(\frac{L/2 - x}{\sqrt{4\alpha(t - t')}}\right) \right]$$

$$\cdot \left[ erf\left(\frac{W/2 + y}{\sqrt{4\alpha(t - t')}}\right) + erf\left(\frac{W/2 - y}{\sqrt{4\alpha(t - t')}}\right) \right]$$

$$\cdot \left[ erf\left(\frac{z + D + H}{\sqrt{4\alpha(t - t')}}\right) + erf\left(\frac{-D - z}{\sqrt{4\alpha(t - t')}}\right) + erf\left(\frac{z - D}{\sqrt{4\alpha(t - t')}}\right) \right] dt'$$

$$+ erf\left(\frac{z - D}{\sqrt{4\alpha(t - t')}}\right) + erf\left(\frac{D + H - z}{\sqrt{4\alpha(t - t')}}\right) dt'$$

$$(2.10)$$

where g(x', y', z', t') = g(t') = P(t')/V, since the power dissipation is assumed to be uniform. Equation (2.10) represents the temperature response at any point in the device at time t due to a change in continuous power dissipation in the base/collector SCR. Assuming a step increase in power at t' = 0 ( $P(t') = P \cdot U(t)$ ) and expressing the temperature rise as

$$\Delta T(t) = Z_{TH}(t) \cdot P \tag{2.11}$$

yields the transient thermal impedance

$$Z_{TH}(x, y, z, t) = \int_{t}^{1} \frac{1}{8\rho cV} \left[ erf\left(\frac{L/2 + x}{\sqrt{4\alpha t}}\right) + erf\left(\frac{L/2 - x}{\sqrt{4\alpha t}}\right) \right]$$

$$\cdot \left[ erf\left(\frac{W/2 + y}{\sqrt{4\alpha t}}\right) + erf\left(\frac{W/2 - y}{\sqrt{4\alpha t}}\right) \right]$$

$$\cdot \left[ erf\left(\frac{z + D + H}{\sqrt{4\alpha t}}\right) + erf\left(\frac{-D - z}{\sqrt{4\alpha t}}\right) + erf\left(\frac{z - D}{\sqrt{4\alpha t}}\right) + erf\left(\frac{D + H - z}{\sqrt{4\alpha t}}\right) \right] dt \qquad (2.12)$$

where the  $t\to\infty$  value of the thermal impedance corresponds to the thermal spreading resistance  $R_{TH}$ .

Equation (2.12) represents the temperature rise at any point in the device normalized to a unit-step increase in power dissipation. For circuit simulation, a single temperature is needed to represent the effective operating temperature of the device. Fox and Lee [Fox91b] showed that the thermal impedance model evaluated at a surface corner of the emitter (x = L/2, y = W/2, z = 0) agreed well with measurements of the thermal spreading resistance  $R_{TH}$ ; substituting these coordinates into (2.12) gives the following expression for the thermal impedance

$$Z_{TH}(t) = \int_{t} \frac{1}{4\rho c V} erf\left(\frac{L}{\sqrt{4\alpha t}}\right) erf\left(\frac{W}{\sqrt{4\alpha t}}\right) \left[erf\left(\frac{D+H}{\sqrt{4\alpha t}}\right) - erf\left(\frac{D}{\sqrt{4\alpha t}}\right)\right] dt . \quad (2.13)$$

In this form, the thermal impedance model has four geometric input parameters. Of the four, three (W, L and D) are determined directly by the device layout. However, the fourth parameter, H, depends on the operating bias of the device. The thickness of the base/collector SCR, H, can be estimated using the

depletion approximation; assuming a one-sided step junction with uniform doping on each side gives

$$H = \sqrt{\frac{2 \cdot \varepsilon_{Si} \cdot \varepsilon_0 \cdot (V_R + \Psi_{bi})}{q \cdot N_{epi}}},$$

(2.14)

with

$$\Psi_{bi} = \frac{k_B \cdot T}{q} \cdot \ln \left( \frac{N_b \cdot N_{epi}}{n_i^2} \right), \tag{2.15}$$

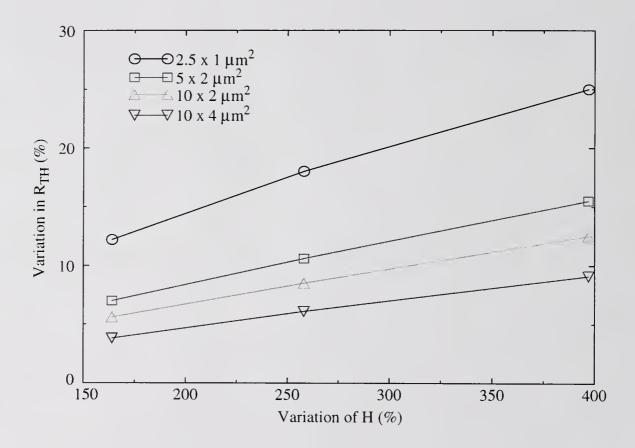

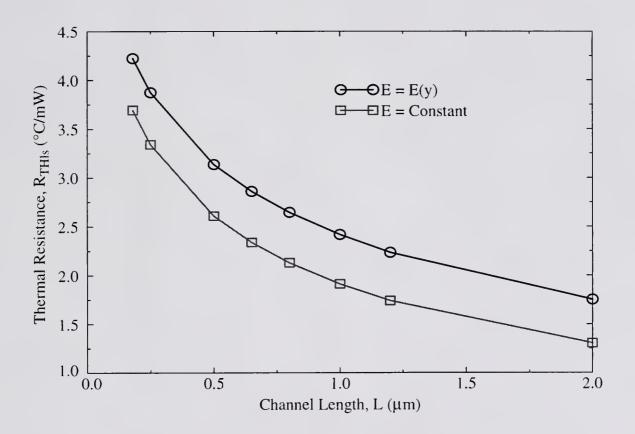

where  $\epsilon_{Si}$  is the dielectric constant of silicon,  $\epsilon_0$  is the permittivity of free space,  $V_R$ is the reverse bias voltage on the base/collector junction, q is electronic charge, N<sub>eni</sub> is the doping level in the epi-collector, k<sub>B</sub> is Boltzman's constant, T is temperature, N<sub>b</sub> is the doping level in the base, and n<sub>i</sub> is the intrinsic carrier concentration in silicon.  $\Psi_{bi}$  is the built-in potential of the base/collector junction. Equation (2.14) shows that the thermal impedance depends on the bias of the base/collector junction, and therefore can change during device operation. However, the square-root dependence of H on the base/collector voltage, is relatively weak. Figure 2.3 illustrates the variation of the modeled thermal resistance with changes in the thickness of the base/collector SCR. The three data points plotted for each simulated device correspond to reverse bias base/collector voltages of 5, 10 and 20 V. The largest variation is observed for the smallest device, which shows a 25% change in its thermal resistance going from  $V_R = 0 V$  to 20 V. The larger devices show a weaker dependence on H and have no more than a 15% change in thermal resistance

Figure 2.3 Simulations showing the effect of variations in the thickness of the base/collector space-charge region on the thermal impedance model (evaluated at steady-state) for different geometry BJTs. For each device, D = 0.35  $\mu$ m, N<sub>epi</sub> = 1 x 10<sup>16</sup> cm<sup>-3</sup> and N<sub>b</sub> = 1.5 x 10<sup>18</sup> cm<sup>-3</sup>. The y-axis corresponds to the variation between the model evaluated at V<sub>R</sub> = 0 V and the model evaluated at V<sub>R</sub> equal to 5, 10 and 20 V.

going from  $V_R = 0$  V to 20 V. However, at high base/collector biases, the maximum value of H becomes effectively independent of bias. As shown in Figure 2.1, typical bipolar technologies use a heavily-doped buried layer to reduce collector resistance. At high base/collector biases, the low-doped epi-collector region depletes down to the buried layer; consequently, the maximum value of H should be properly limited to the thickness of the epi-collector.

#### 2.2.1 Modification for Finite Wafer Thickness

As previously derived, the thermal impedance model for single-emitter bulk BJT/HBT's represents the substrate as a semi-infinite half-space. This representation assumes that the back side of the substrate does not affect the thermal response of the device. In general, this is reasonable since the base-collector junction is usually within 1 µm of the substrate surface, and a typical wafer is between 350 to 800 µm thick. However, wafers are commonly back-lapped to improve thermal performance, and substrate thicknesses of 75, 80 and 100 µm have been reported by a number of authors [Kag94, Mar93, Liu95a]. As the wafer thickness is reduced, the substrate can no longer be approximated by a semi-infinite medium and the effects of the back-side boundary must be taken into account.

The three-dimensional Green's function in the rectangular coordinate system can be represented by the product of three one-dimensional Green's functions

$$G(x, y, z, t|x', y', z', t') = G_{x}(x, t|x', t') \cdot G_{y}(y, t|y', t') \cdot G_{z}(z, t|z', t'). \tag{2.16}$$

The lateral boundaries are still assumed to extend infinitely and their effects on the thermal response are neglected; thus, the Green's function solutions in both the x and y directions remain unchanged. In the z-direction, however, the substrate is now assumed to have a finite thickness  $D_{sub}$ . The top surface of the substrate is still assumed to be adiabatic. The bottom surface of the substrate is assumed to be at a constant temperature,  $T(D_{sub}) = T_0$ , so that the temperature rise at this surface is defined by  $\Delta T(D_{sub}) = T(D_{sub}) - T_0 = 0$ . These boundary conditions define the new Green's function for the z-direction, which is given by

$$G_{z}(z, t|z', t') = \sum_{p=1}^{\infty} \exp[-\alpha \cdot \eta_{p}^{2}(t-t')] \cdot \frac{2}{D_{sub}} \cdot \cos(\eta_{p}z) \cdot \cos(\eta_{p}z')$$

(2.17)

where  $\eta_p$  is the set of eigenvalues for the boundary-value problem and are given by the positive roots of

$$\cos(\eta_p D_{sub}) = 0. \tag{2.18}$$

Equation (2.18) is solved when the argument of the cosine equates to odd multiples of  $\pi/2$ . Using equations (2.17), (2.16), (2.11) and (2.7), and then integrating over the base/collector SCR, assuming a unit-step increase in power at t' = 0, gives the following expression for the thermal impedance at any point in the device

$$Z_{TH}(x, y, z, t) = \int_{t}^{t} \frac{dt}{4\rho c V} \left[ erf\left(\frac{L/2 + x}{\sqrt{4\alpha t}}\right) + erf\left(\frac{L/2 - x}{\sqrt{4\alpha t}}\right) \right]$$

$$\cdot \left[ erf\left(\frac{W/2 + y}{\sqrt{4\alpha t}}\right) + erf\left(\frac{W/2 - y}{\sqrt{4\alpha t}}\right) \right]$$

$$\cdot \sum_{p=1}^{\infty} \frac{2\cos(\eta_{p}z)\exp(-\alpha\eta_{p}^{2}t)}{\eta_{p}D_{sub}}$$

$$\cdot \left\{ \sin[\eta_{p}(D + H)] - \sin[\eta_{p}D] \right\}$$

(2.19)

where  $V = W \cdot L \cdot H$  and

$$\eta_{p} = \frac{(2p-1)\pi}{2D_{sub}}.$$

(2.20)

Evaluating (2.19) at the coordinates (x = L/2, y = W/2, z = 0) to give a single effective operating temperature, results in the following expression for the thermal impedance

$$Z_{TH}(t) = \int_{t}^{\infty} \frac{dt}{4\rho c V} erf\left(\frac{L}{\sqrt{4\alpha t}}\right) erf\left(\frac{W}{\sqrt{4\alpha t}}\right)$$

$$\cdot \sum_{p=1}^{\infty} \frac{2 exp(-\alpha \eta_{p}^{2} t)}{\eta_{p} D_{sub}} \left\{ sin[\eta_{p}(D+H)] - sin[\eta_{p}D] \right\}. \tag{2.21}$$

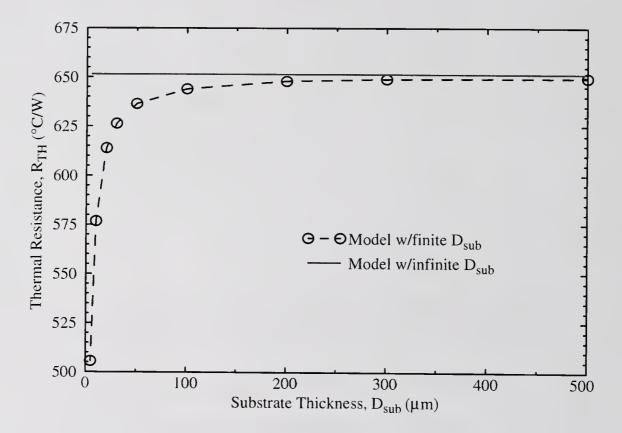

Since (2.21) is derived from the physical heat conduction equation, it can be used to anticipate the effects of substrate scaling on the thermal impedance. Figure 2.4 illustrates equation (2.21) evaluated at various values for  $D_{\rm sub}$ . The results show that the thermal resistance decreases as the substrate thickness is reduced, which agrees with the trend predicted by Hattori et al. using a three-dimensional numerical simulator [Hat95]. Figure 2.4 also shows that (2.13) provides

Figure 2.4 Simulations showing the effect of substrate thickness on the thermal impedance model (evaluated at steady-state). The model accounting for finite substrate thickness is compared to the model assuming infinite substrate thickness. The device specifications are  $L=4~\mu m,$   $W=1~\mu m,$   $D=0.35~\mu m,$   $H=0.35~\mu m.$

an accurate prediction of the thermal resistance over most of the range of substrate thicknesses; only when the substrate thickness is significantly reduced ( $< 100 \, \mu m$ ), is there a large deviation between the two models.

### 2.2.2 Effects of Interconnect Metallization on the Thermal Impedance

For the derivation of the BJT/HBT thermal impedance model, the surface of the substrate is assumed to be adiabatic. In actual devices, portions of the base, collector and emitter regions are in direct contact with the metallization used to electrically connect different devices on a chip. Since the metallization typically has a high thermal conductivity, it is possible that the heat conduction via the interconnects significantly influences the thermal response of a device. Therefore, the validity of such an assumption should be investigated.

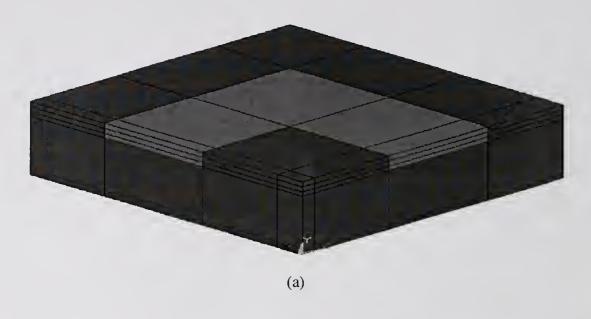

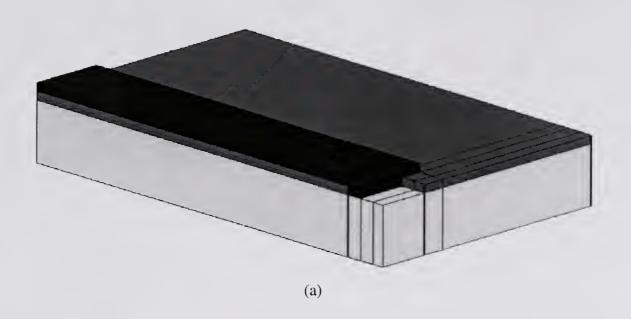

Three-dimensional (3-D) finite-element (FE) thermal simulations of a bipolar transistor, using the ANSYS software package [Ans96], were performed to examine the effects of the interconnect metallization on the thermal impedance. To simplify the FE model, the device was considered to be symmetric in both lateral directions; therefore, only one quarter of the device was simulated. The bottom and exterior sides of the substrate were assumed to be at a fixed ambient temperature. The top and side surfaces of the interconnects, as well as the top surface of the inter-layer dielectric, were assumed to be adiabatic. The FE simulations tend to overpredict the heat conduction through the interconnects since any contact resistances at the material interfaces were neglected. The assumed symmetry of the device implies that the base and collector metallization are equidistant from the emitter. In typical

devices, the collector contact is offset a greater distance from the emitter than the base contact. Typical ranges for these offsets are 0.5 to 10 µm between the base and emitter contacts, and 2.5 to 25 µm between the collector and emitter contacts [Gra93]. While the FE model does not exactly represent any actual device structure, it can provide an estimate for the significance of the heat flow through the interconnects as a function of their distance from the active device.

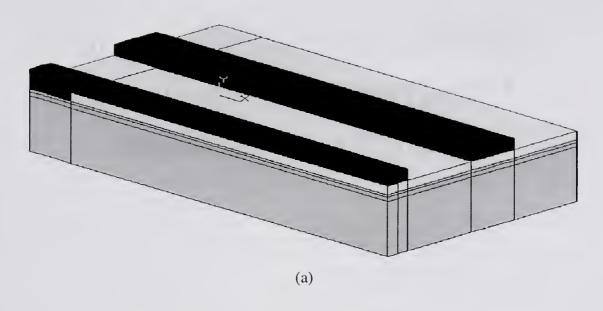

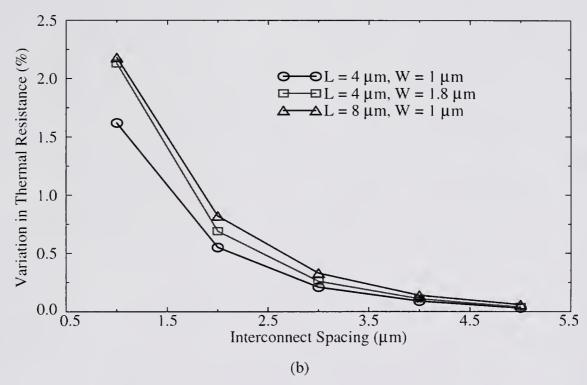

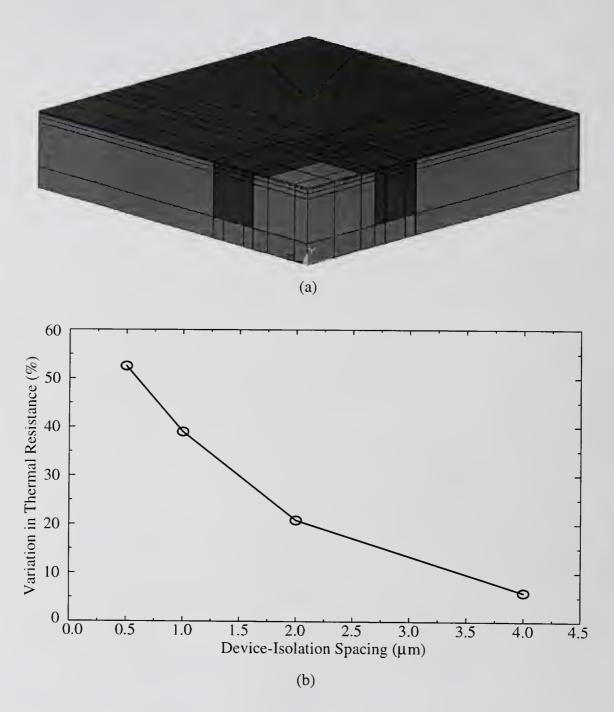

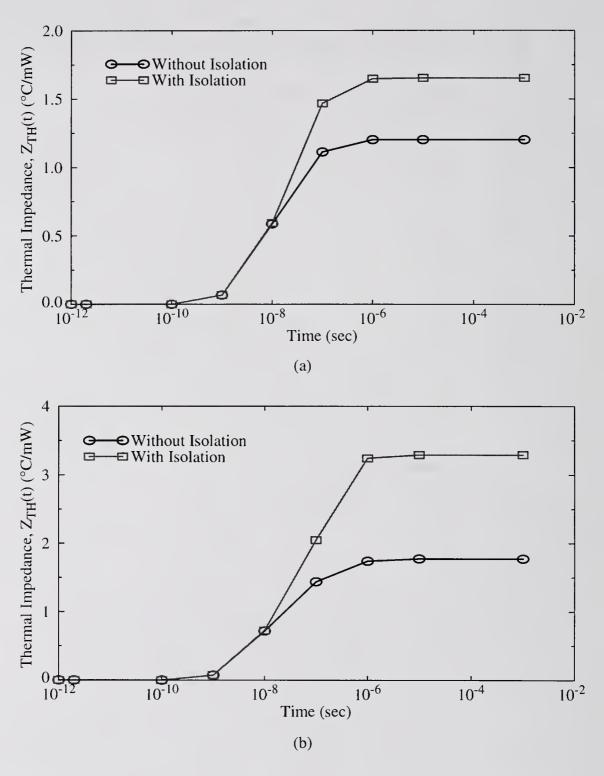

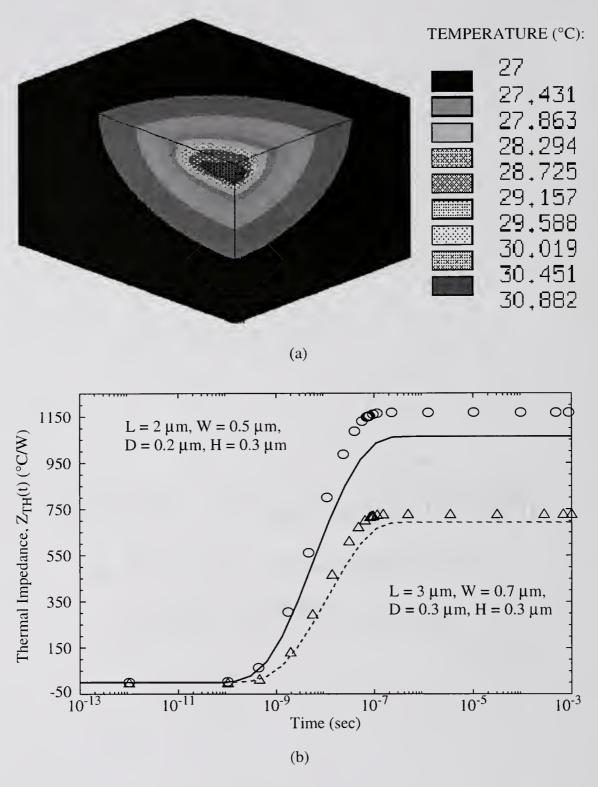

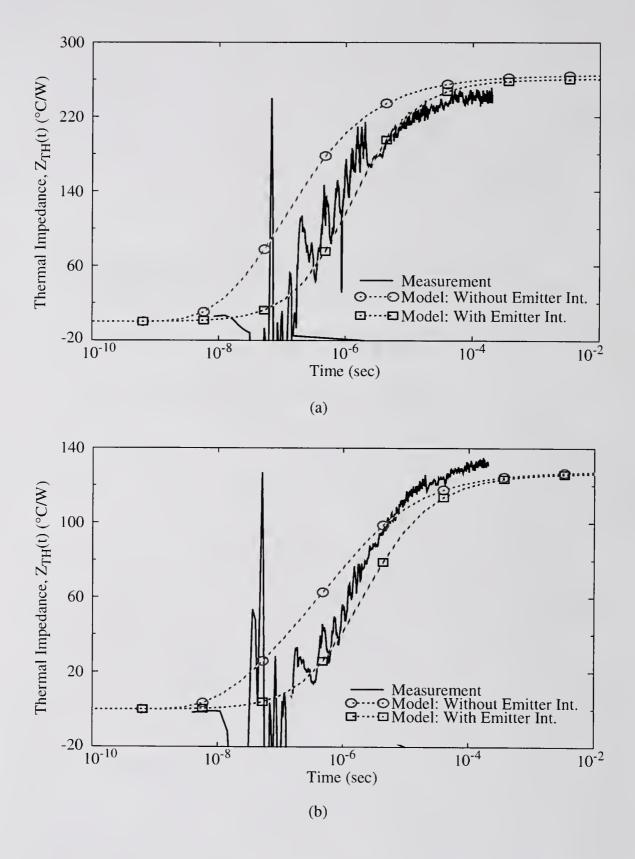

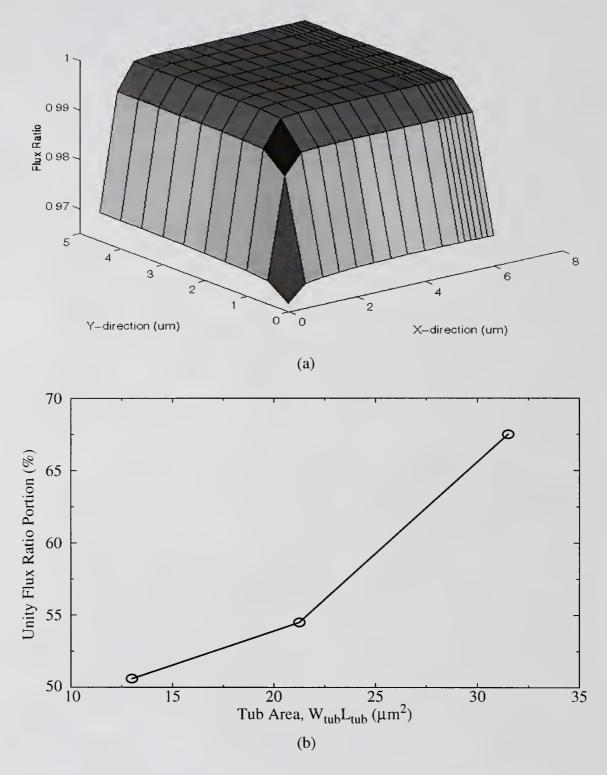

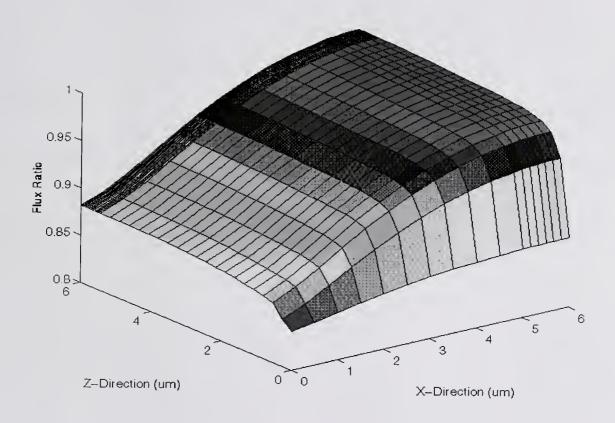

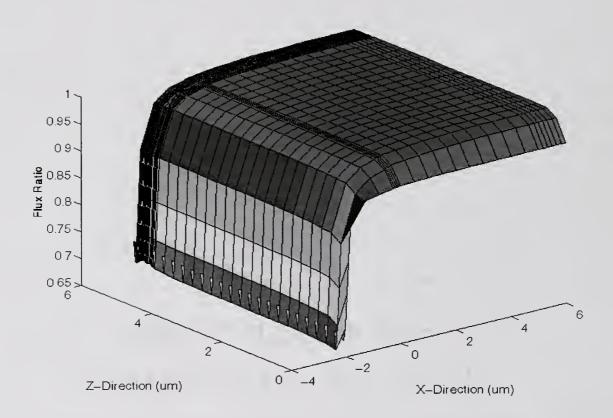

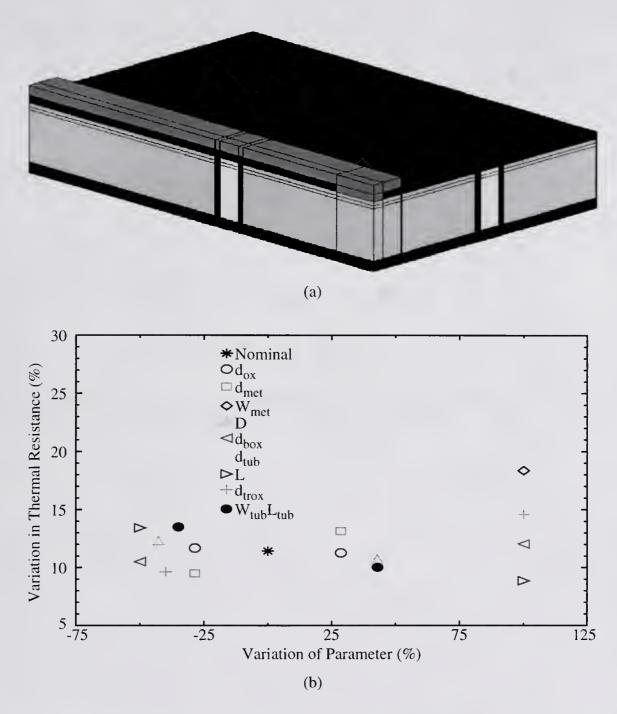

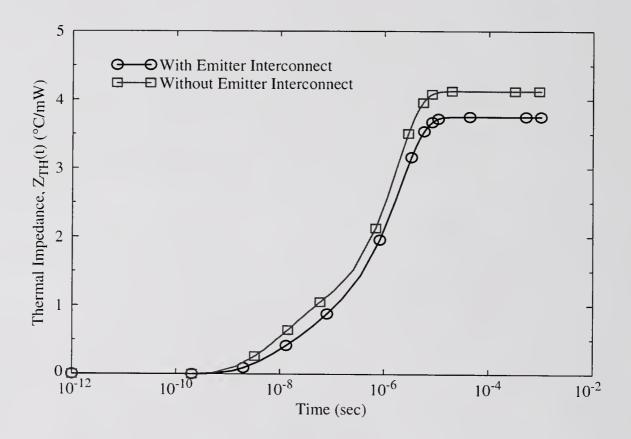

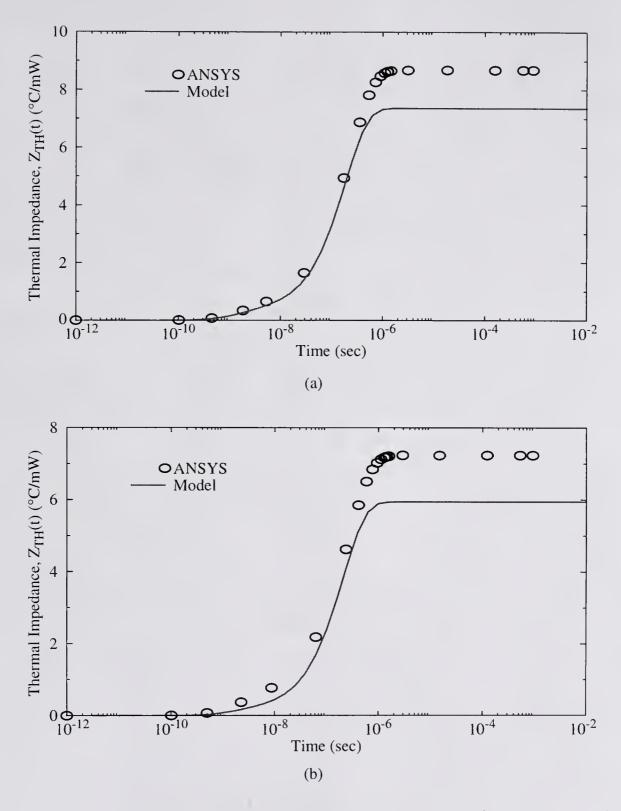

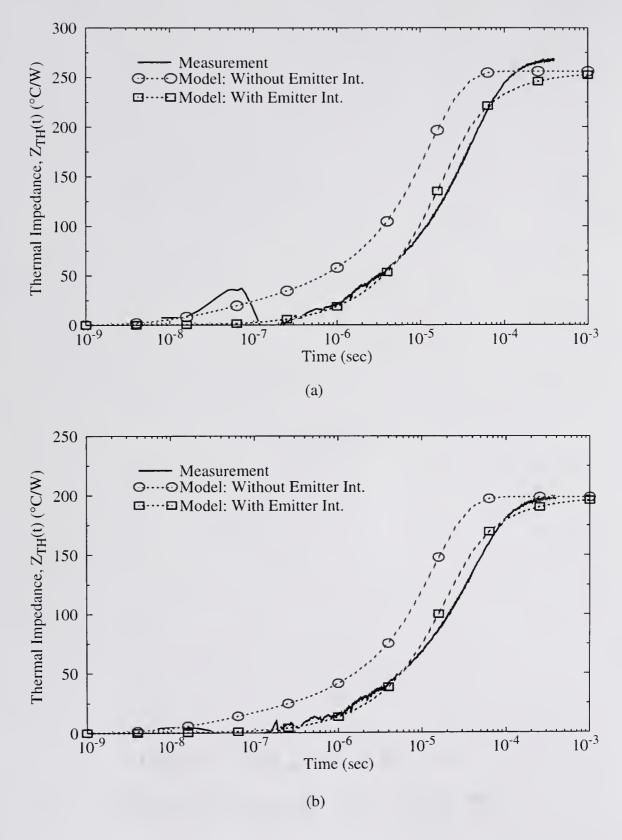

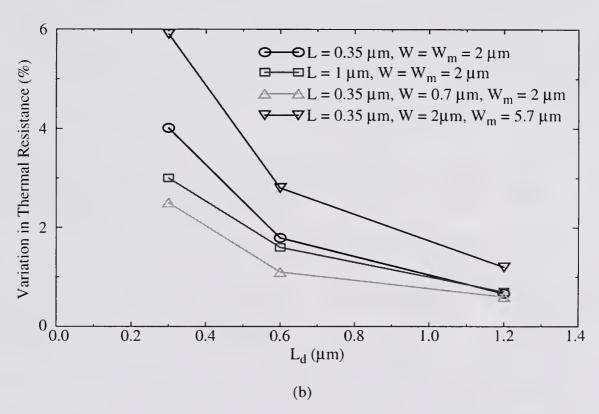

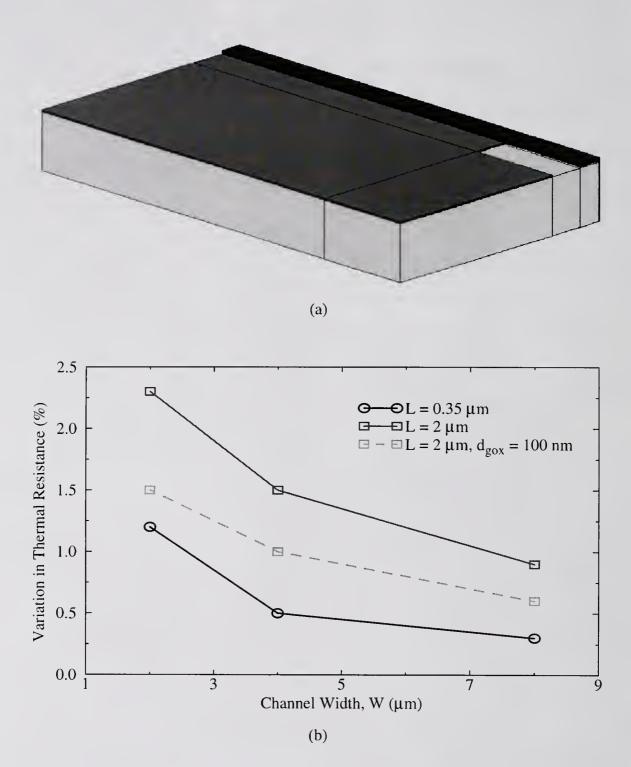

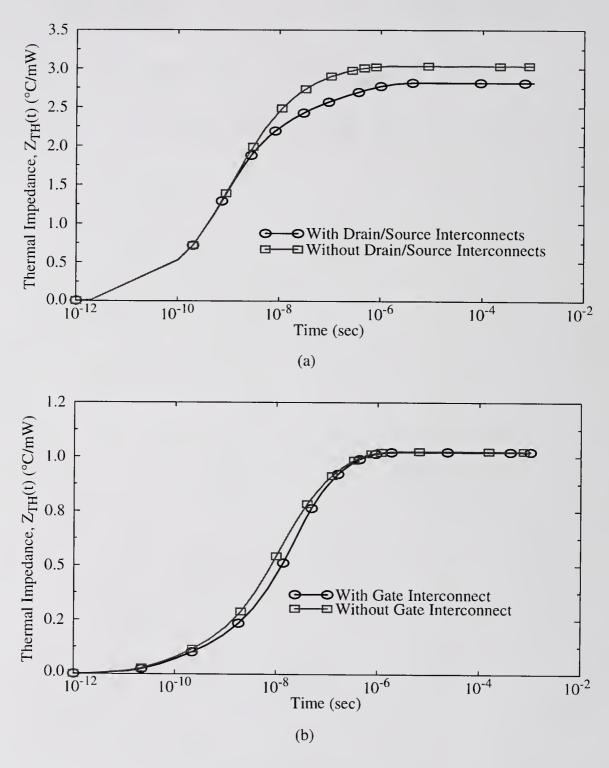

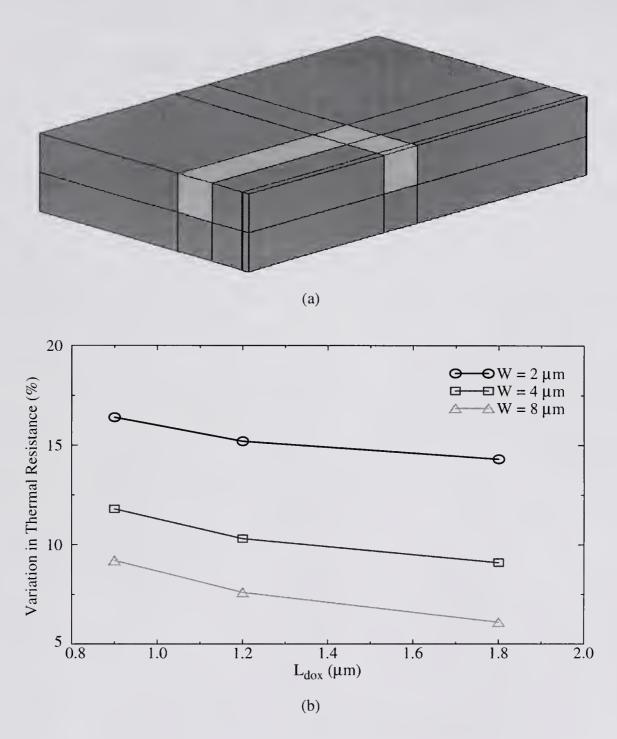

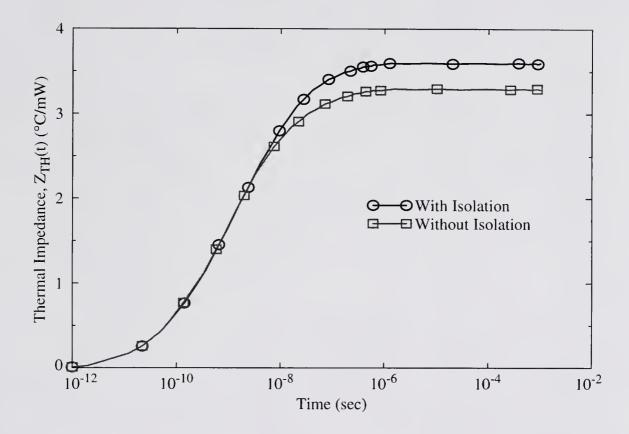

Figure 2.5a shows the FE model for bipolar devices with full metallization. Steady-state thermal simulations were run for various interconnect spacings; this spacing corresponds to the edge-to-edge distance between the emitter and base/collector interconnects. Simulations were also run of the same structure with the base/collector interconnect removed. The results of the two groups of simulations were compared to determine the effect of the base and collector interconnects on the thermal resistance. Figure 2.5b shows the results of the comparison between the FE simulations. The data clearly shows that the effect of the base/collector interconnect metallization is small and decreases as the interconnects are moved away from the active device area. The collector interconnect has less of an effect on the thermal impedance than the base interconnect, due to the larger distance between the collector contact and the active device. In any case, the effect of either the base or collector interconnect should be negligible compared to the influence of the emitter metallization.

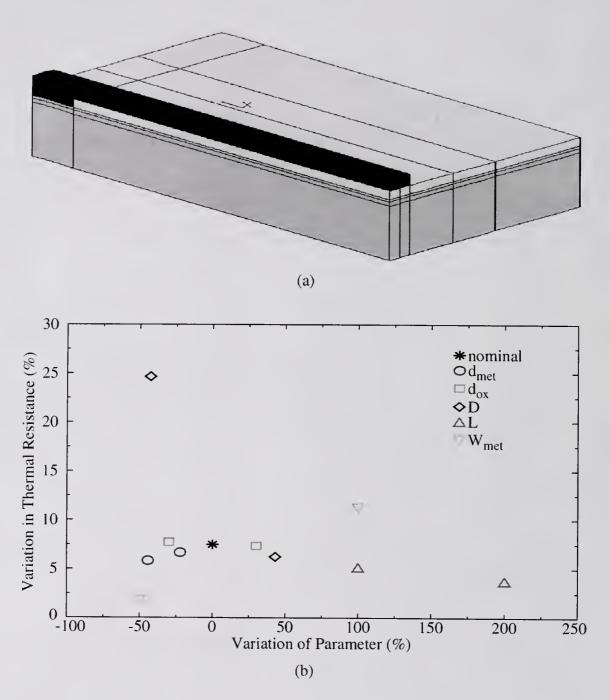

To determine the extent of the effect of the emitter interconnect on the thermal impedance, steady-state thermal simulations were run for different devices with only the emitter metallization in contact with the device. Figure 2.6a shows the

Figure 2.5 ANSYS simulations showing the effect of emitter, base and collector interconnects on the thermal resistance. The device specifications are  $D=0.2~\mu m$  and  $H=0.35~\mu m$ , the interconnect width  $W_{met}=2~\mu m$  and thickness  $d_{met}=0.9~\mu m$ , and the inter-layer dielectric thickness  $d_{ox}=0.7~\mu m$ : a) The finite-element model simulated with ANSYS; b) the variation between the thermal resistance accounting for emitter, base and collector interconnects and the thermal resistance accounting for only the emitter interconnect, plotted as a function of the spacing between emitter and base/collector interconnects.

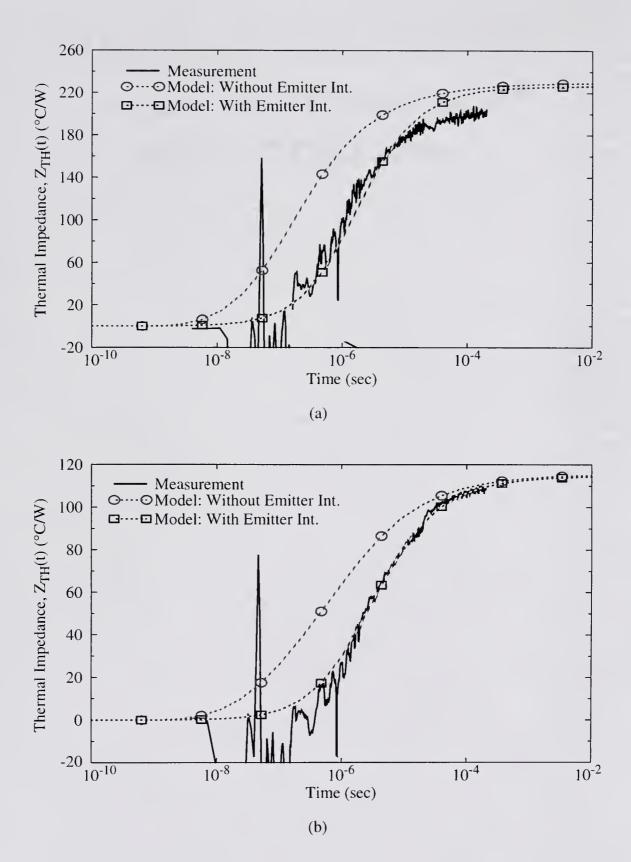

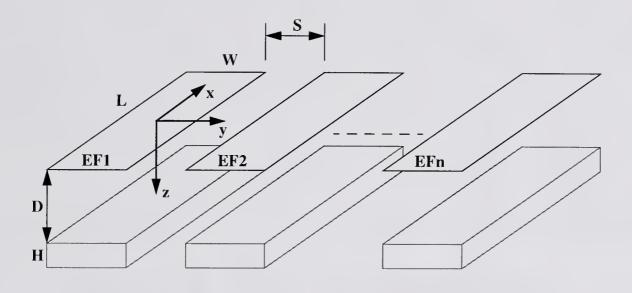

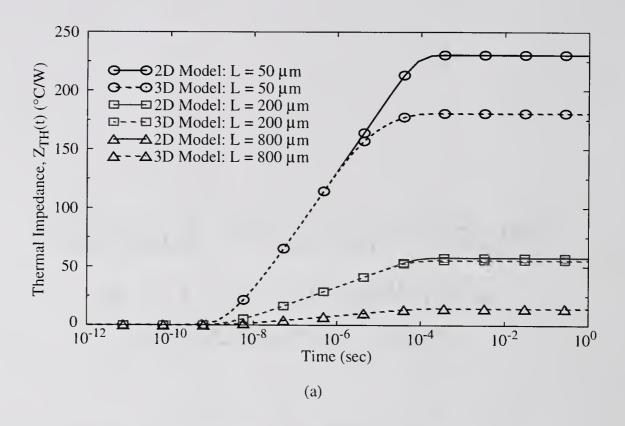

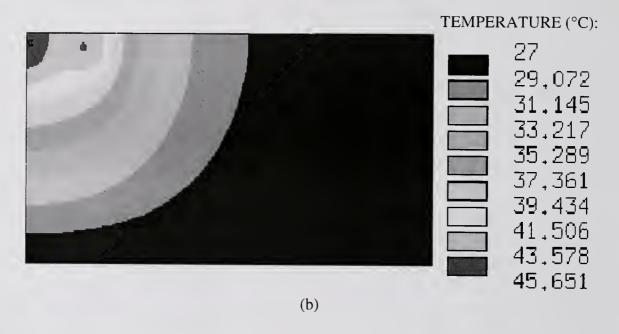

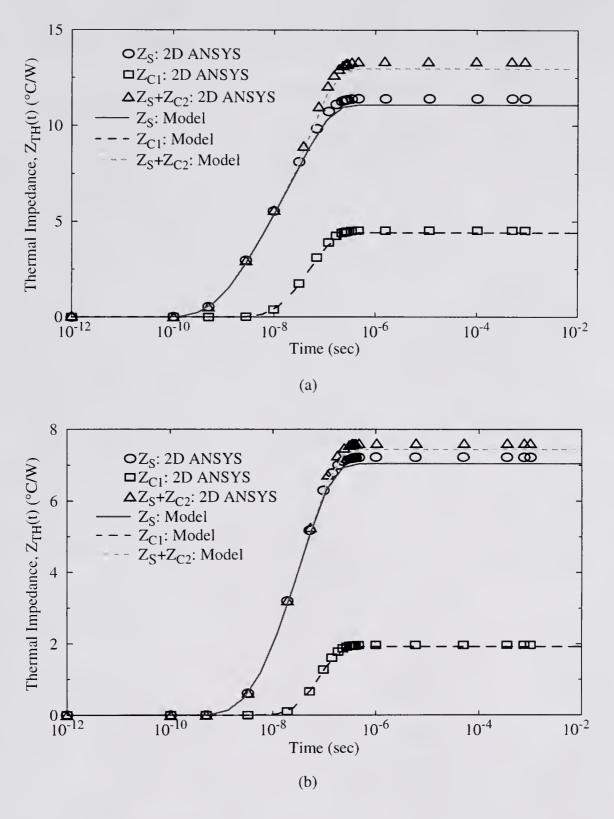

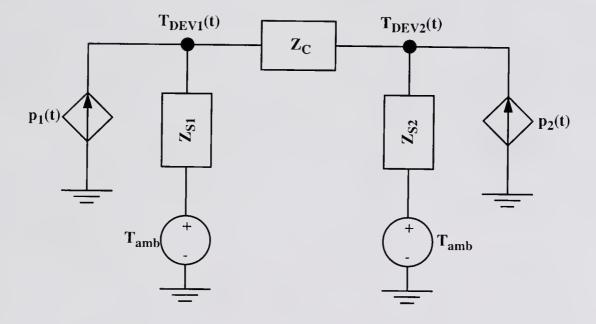

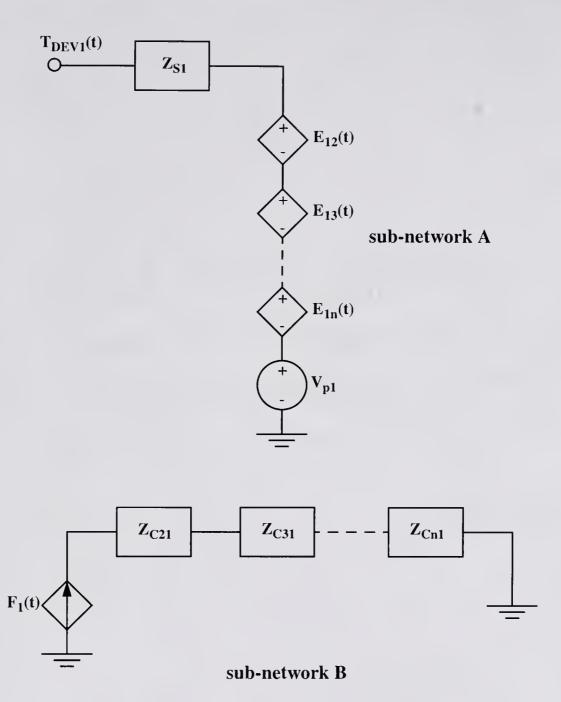

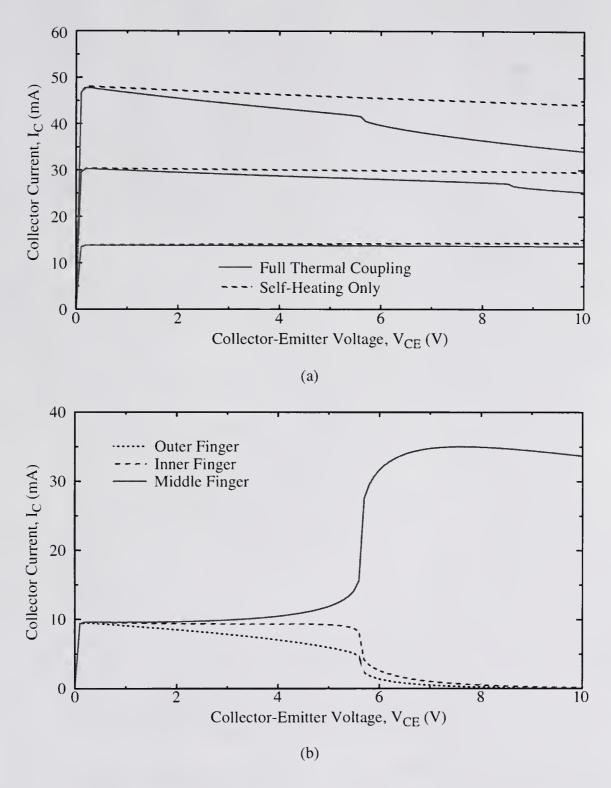

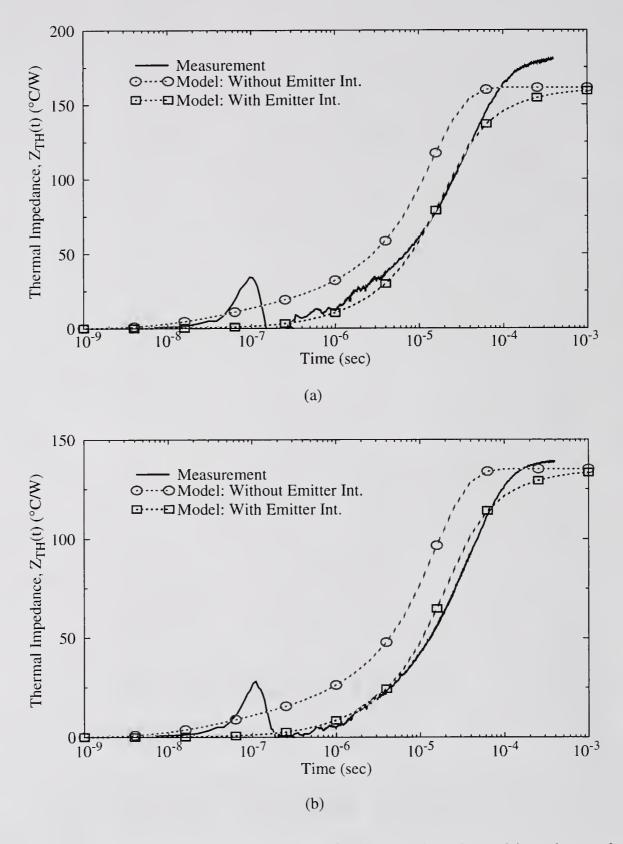

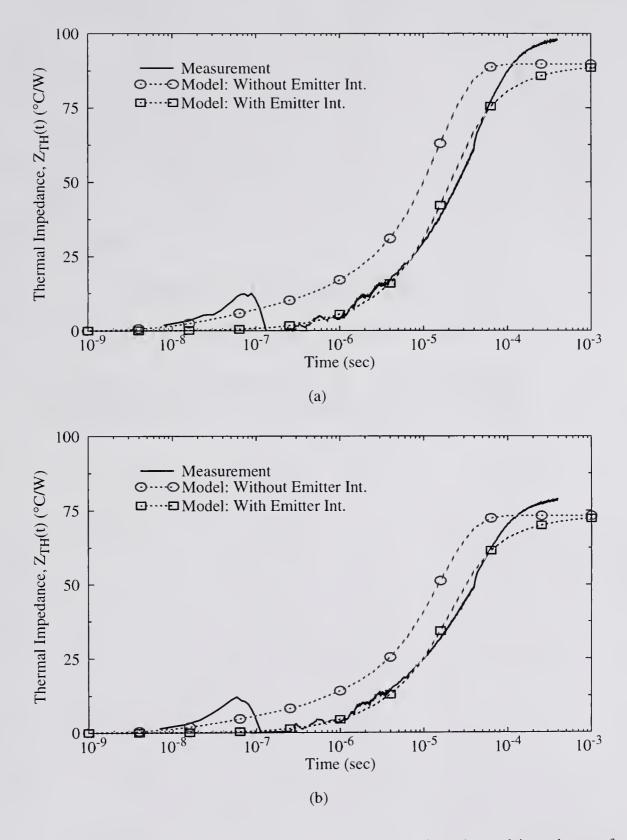

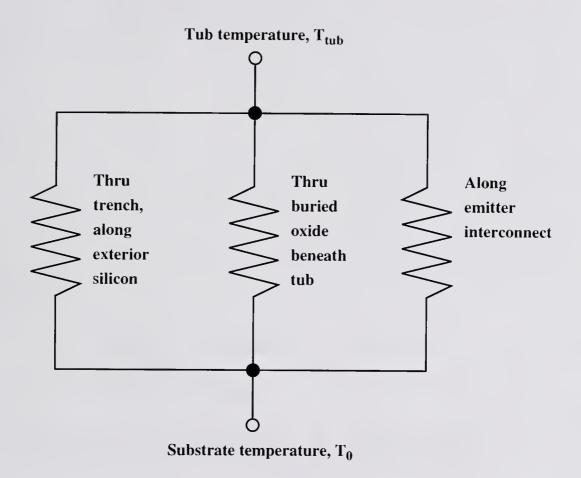

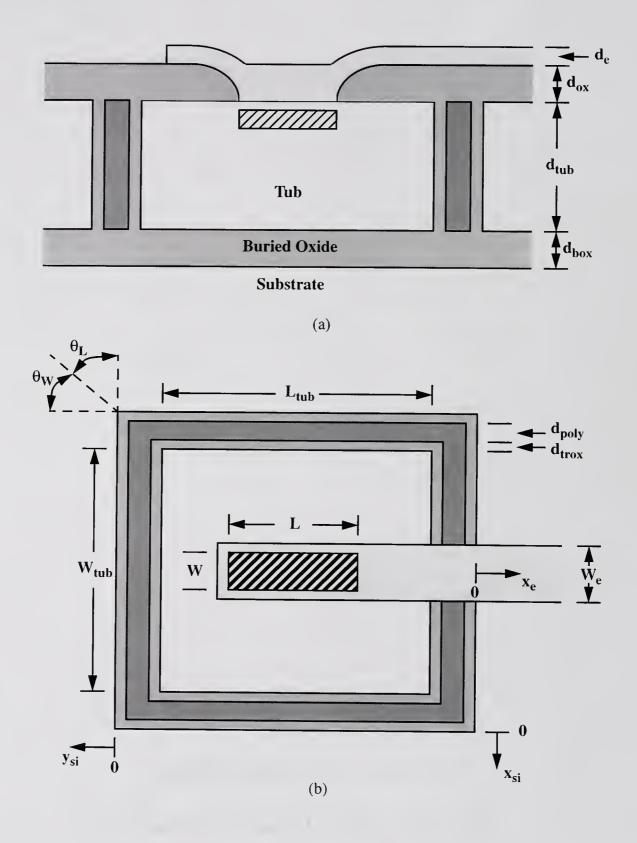

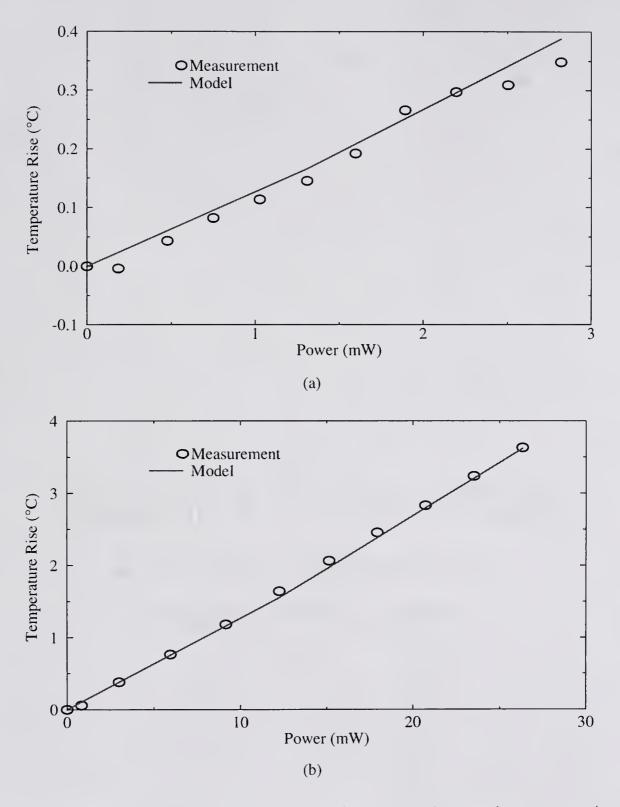

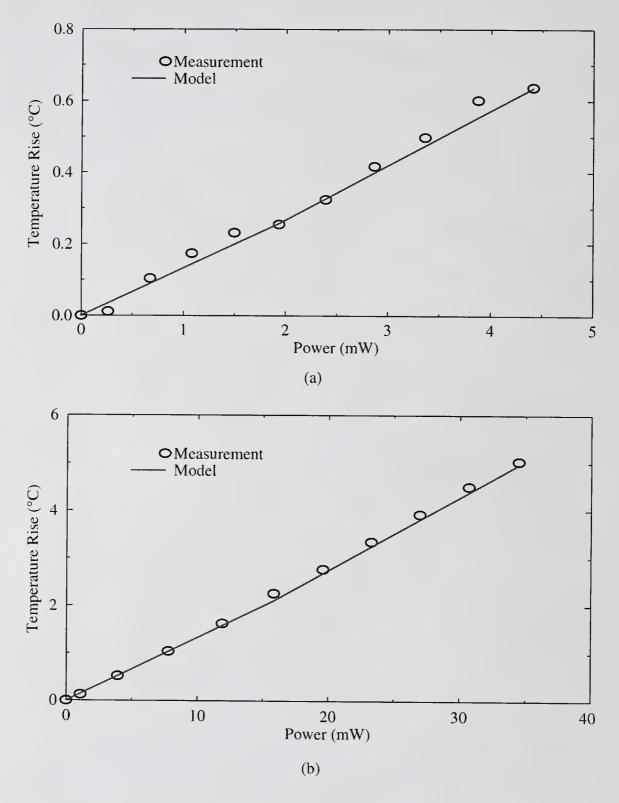

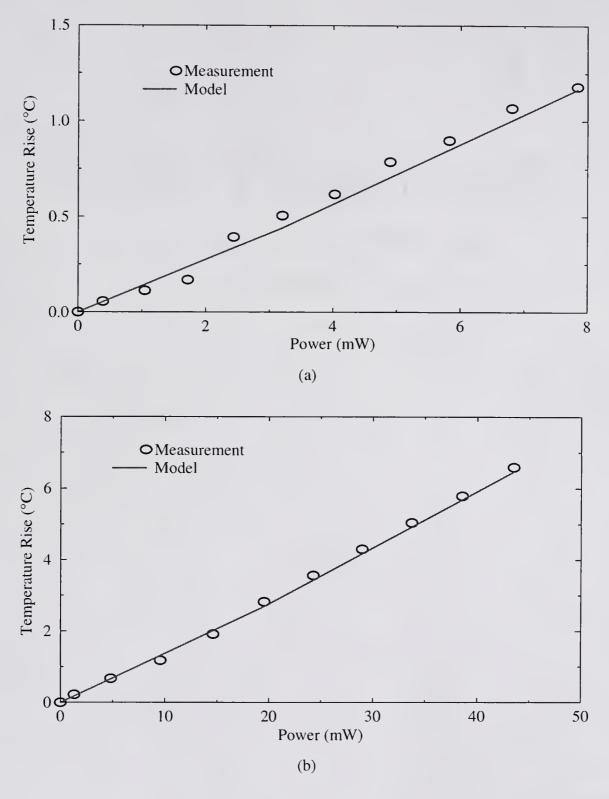

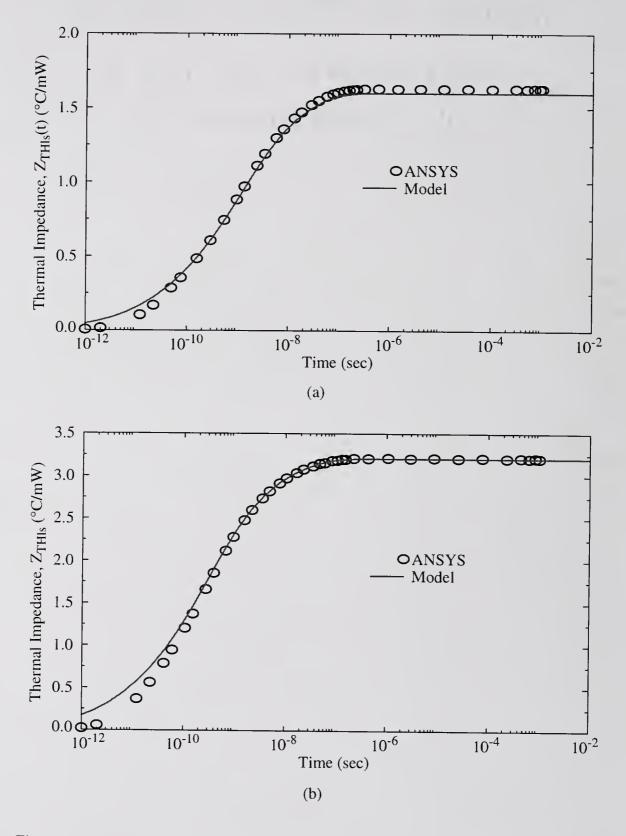

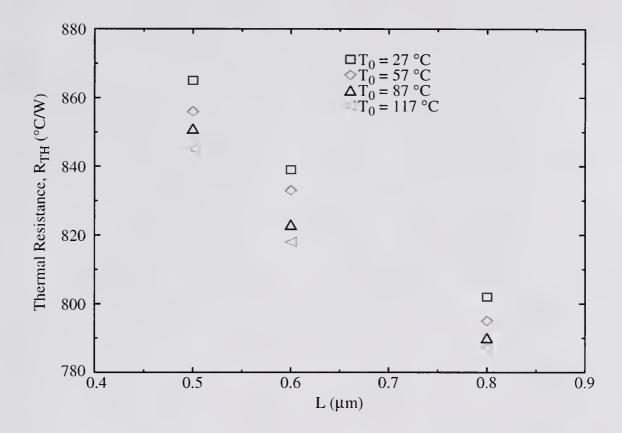

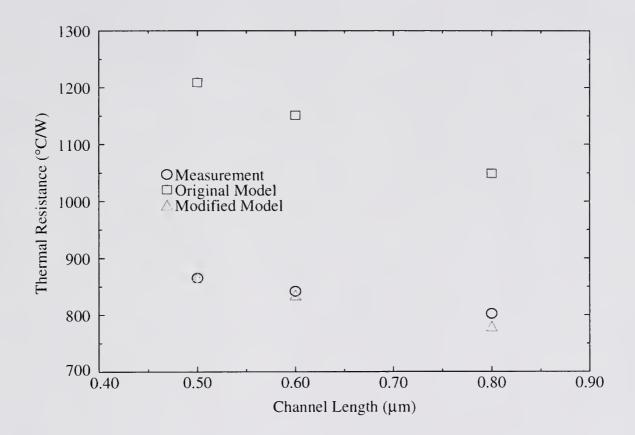

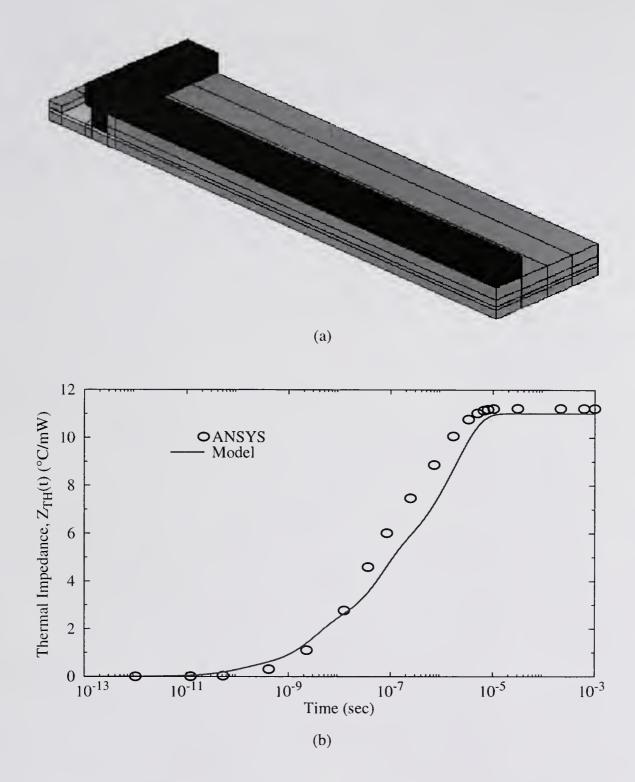

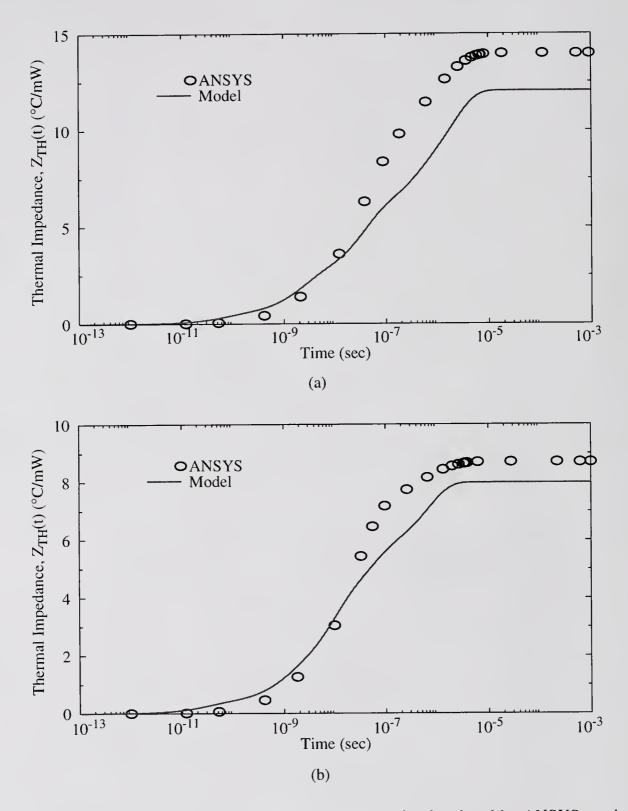

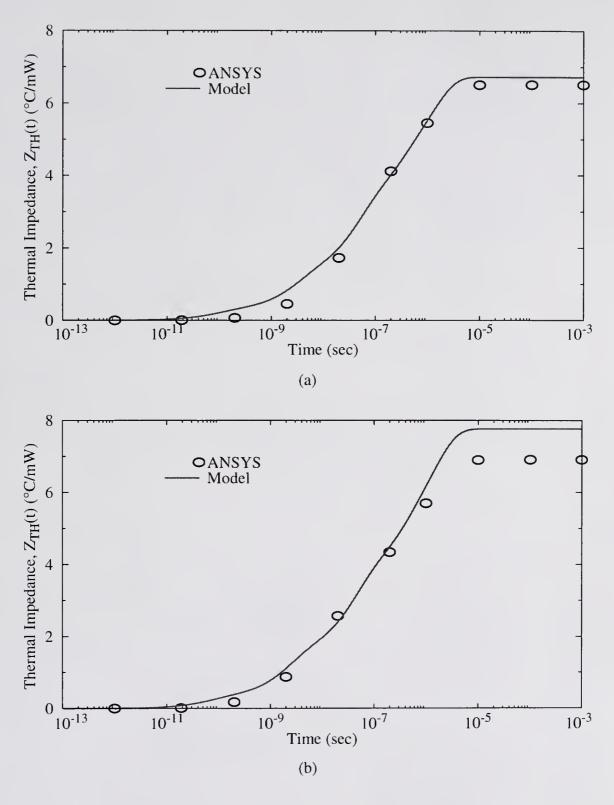

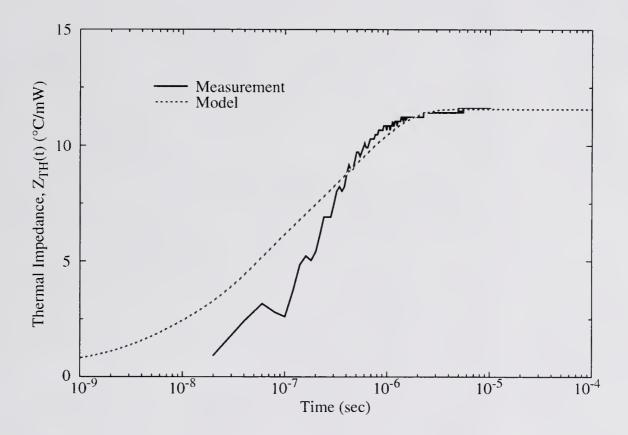

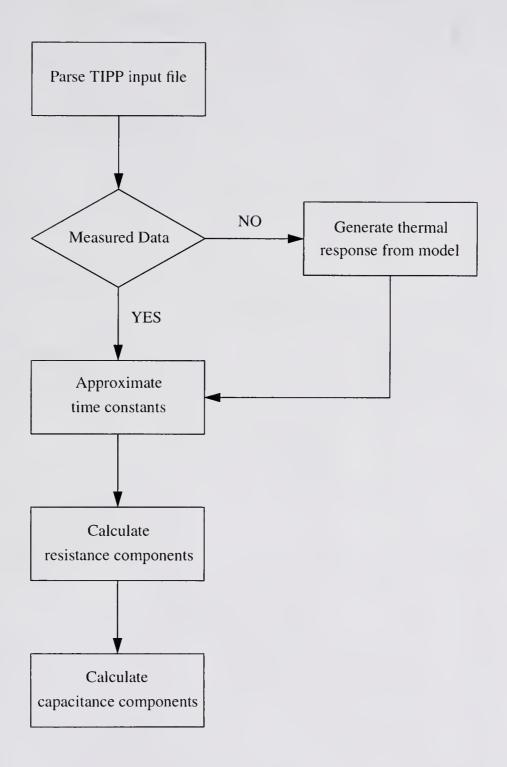

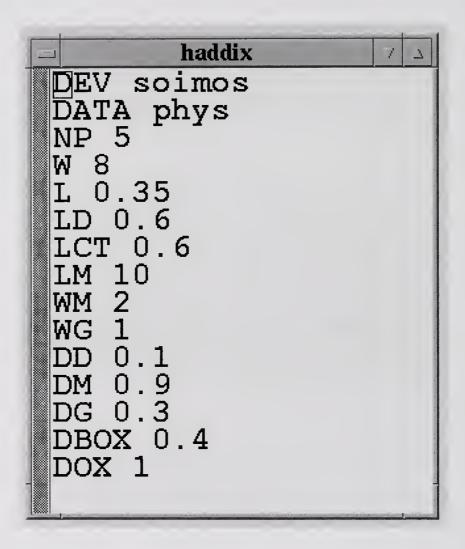

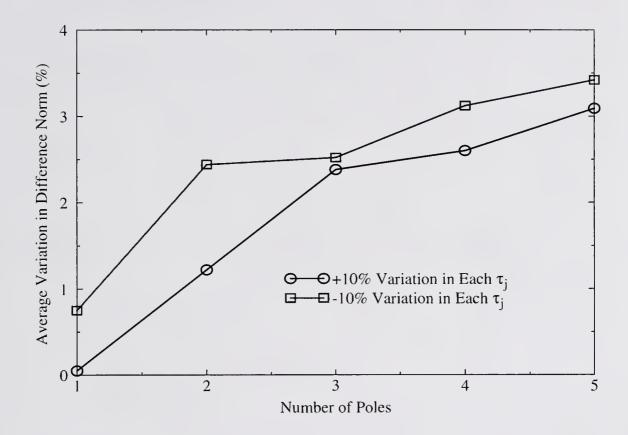

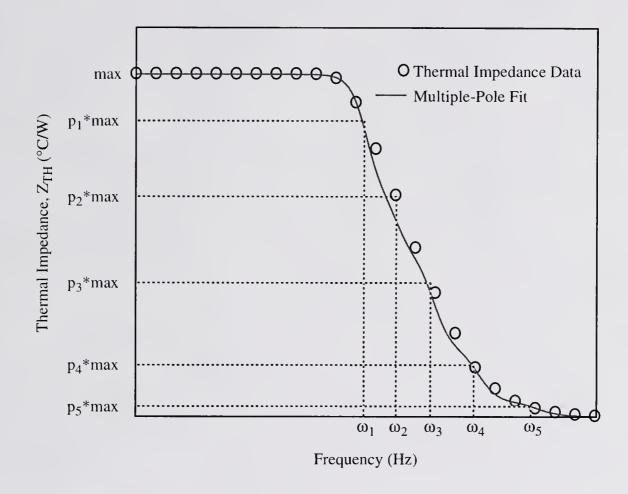

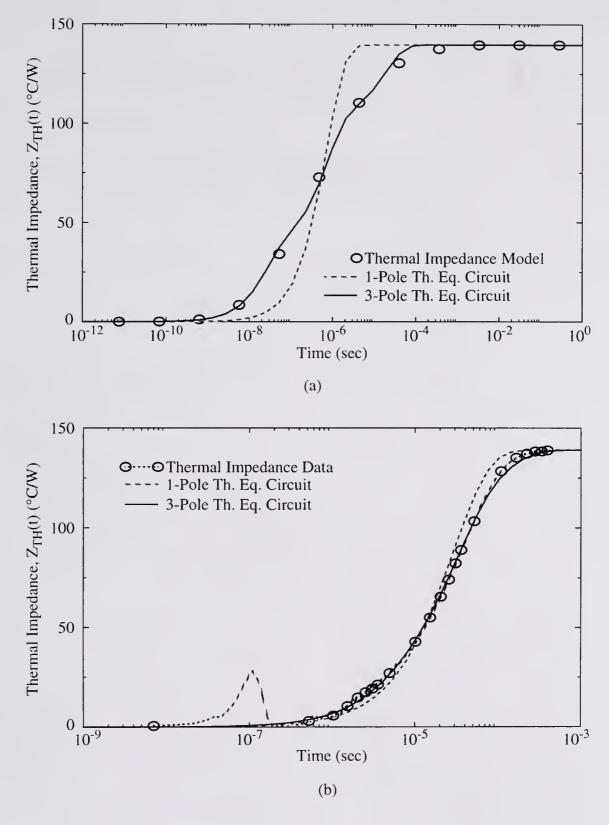

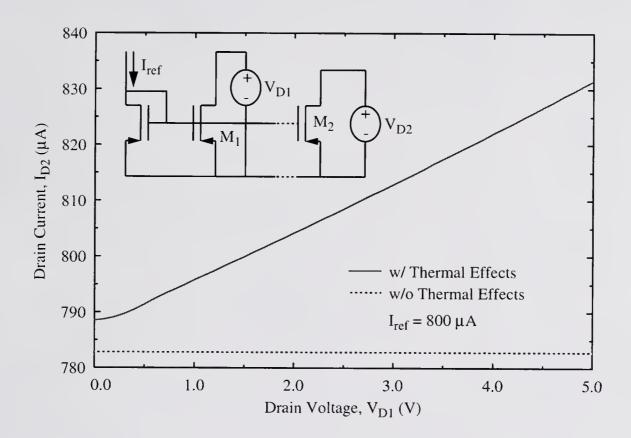

Figure 2.6 ANSYS simulations showing the effect of the emitter interconnect on the thermal resistance for variations in different technology characteristics. The specifications for the nominal device are  $L=4~\mu m,~W=1~\mu m,~D=0.35~\mu m,~H=0.35~\mu m,~d_{met}=0.9~\mu m,~d_{ox}=0.9~\mu m$  and  $W_{met}=2~\mu m$ : a) The finite-element model simulated with ANSYS; b) the variation between the thermal resistance accounting for the emitter interconnect and the thermal resistance neglecting the emitter interconnect. The variation plotted on the x-axis corresponds to the deviation of each structure parameter from its nominal value.